# Arithmetic Logic

adders Arithmetic Logic Unit

https://cs.wellesley.edu/~cs240/

### Motivation: how do we go from code to gates?

```

int count_odds(int array[10]) {

int count = 0;

for (int i = 0; i < 10; i++) {

count += array[i] & 0x1;

}

return count;</pre>

```

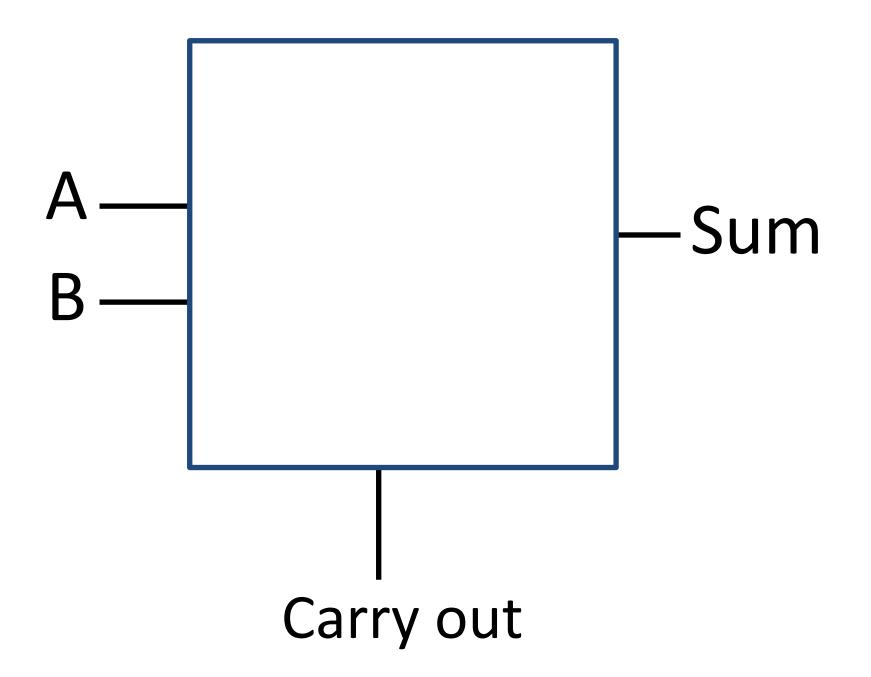

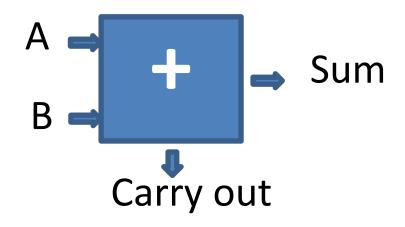

## Addition: 1-bit half adder

Hint: the smallest solution uses 2 gates from: AND, OR, XOR, NOT, NAND, NOR

| Α | B | Carry<br>Out | Sum |

|---|---|--------------|-----|

| 0 | 0 | 0            | 0   |

| 0 | 1 | 0            | 1   |

| 1 | 0 | 0            | 1   |

| 1 | 1 | 1            | 0   |

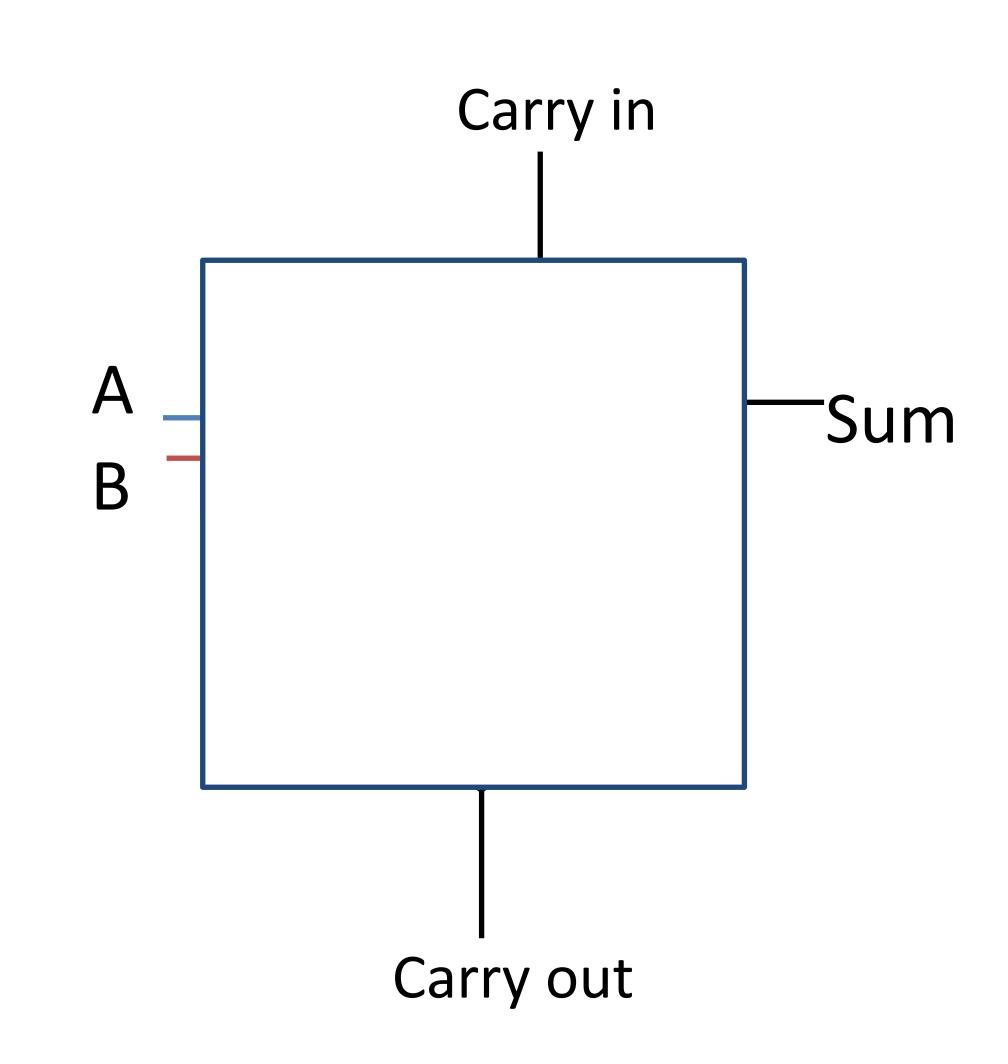

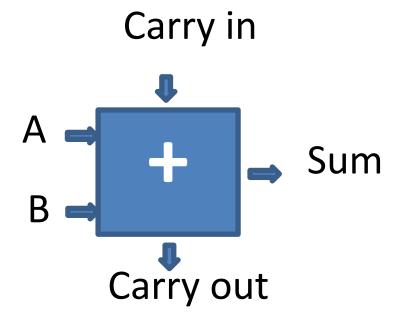

### Addition: 1-bit *full* adder

| Carry<br>in | Α | B | Carry<br>Out | Sum |

|-------------|---|---|--------------|-----|

| 0           | 0 | 0 | 0            | 0   |

| 0           | 0 | 1 | 0            | 1   |

| 0           | 1 | 0 | 0            | 1   |

| 0           | 1 | 1 | 1            | 0   |

| 1           | 0 | 0 | 0            | 1   |

| 1           | 0 | 1 | 1            | 0   |

| 1           | 1 | 0 | 1            | 0   |

| 1           | 1 | 1 | 1            | 1   |

There are faster, more complicated ways too...

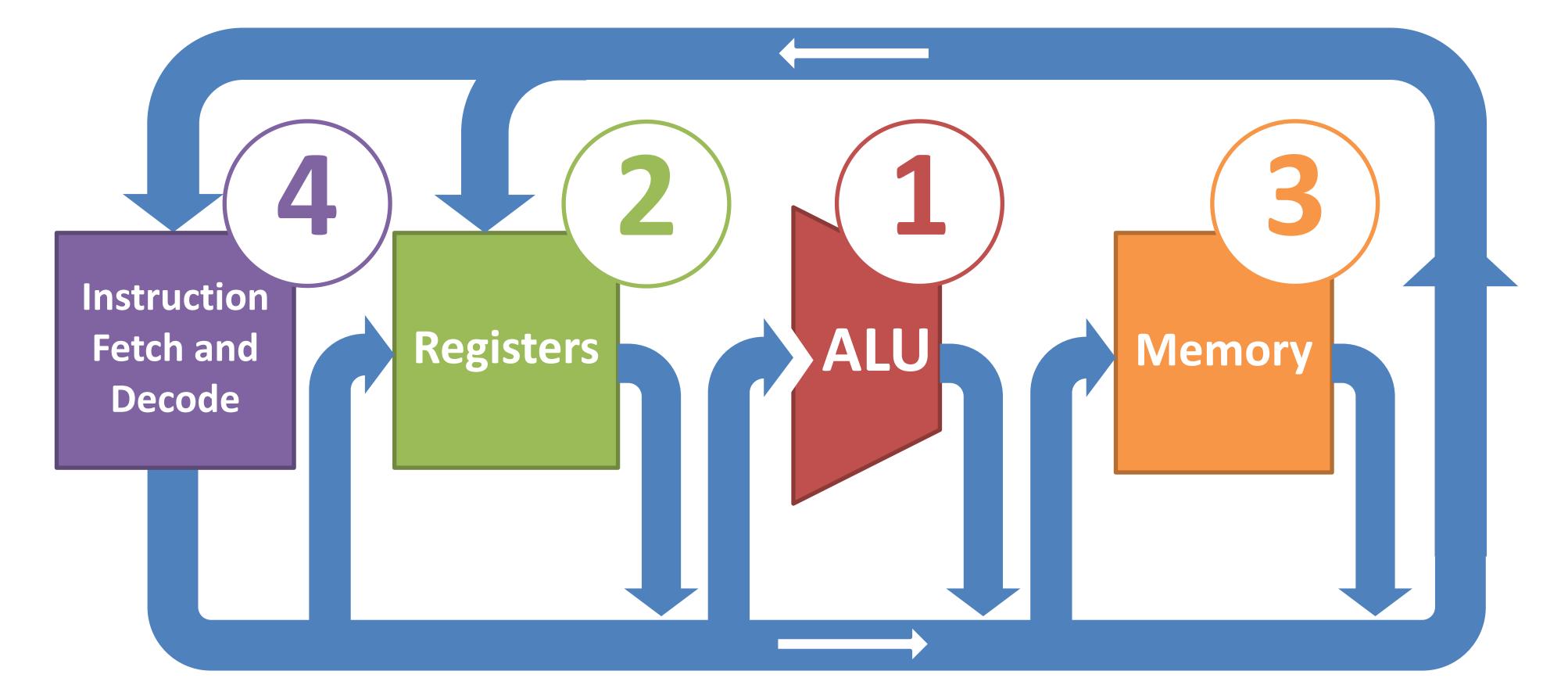

### **Processor Components**

## **Arithmetic Logic Unit (ALU)**

a few bits ----> Operation word ALU Result a few bits **Condition Codes**

(sign, overflow, carry-out, zero)

Hardware unit for arithmetic and bitwise operations.

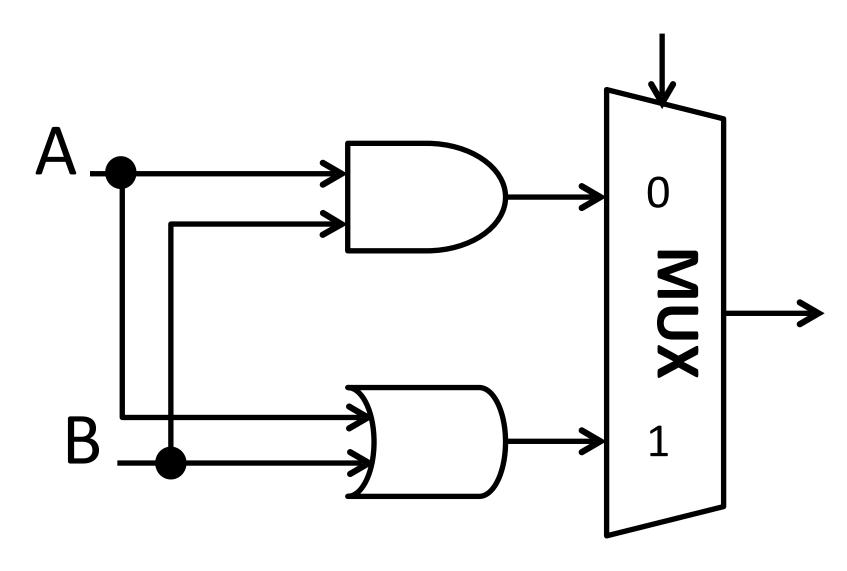

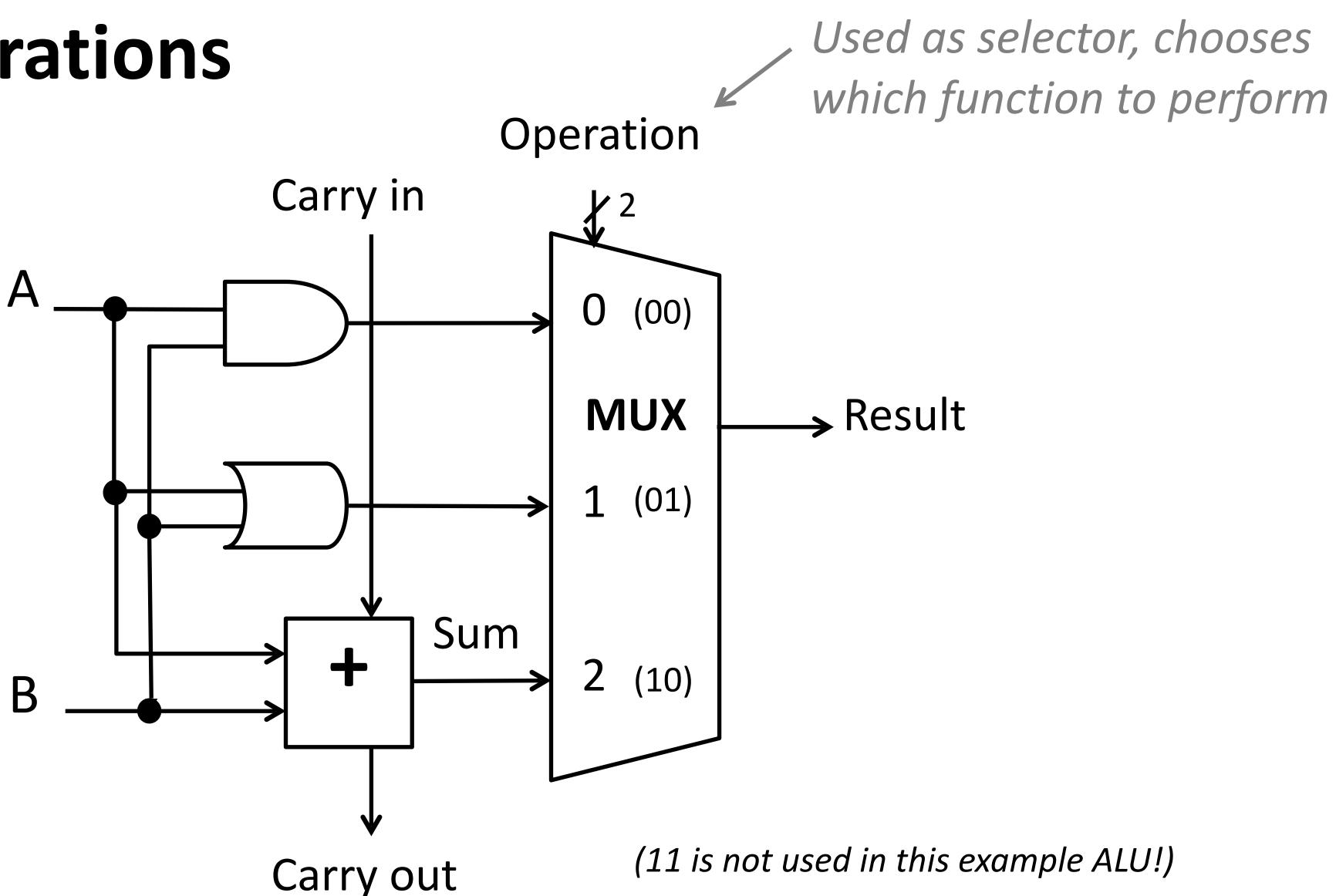

## 1-bit ALU for bitwise operations

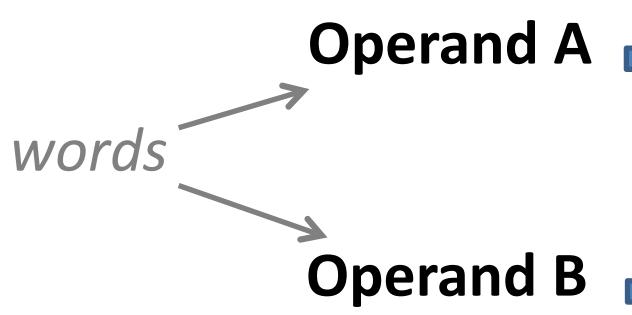

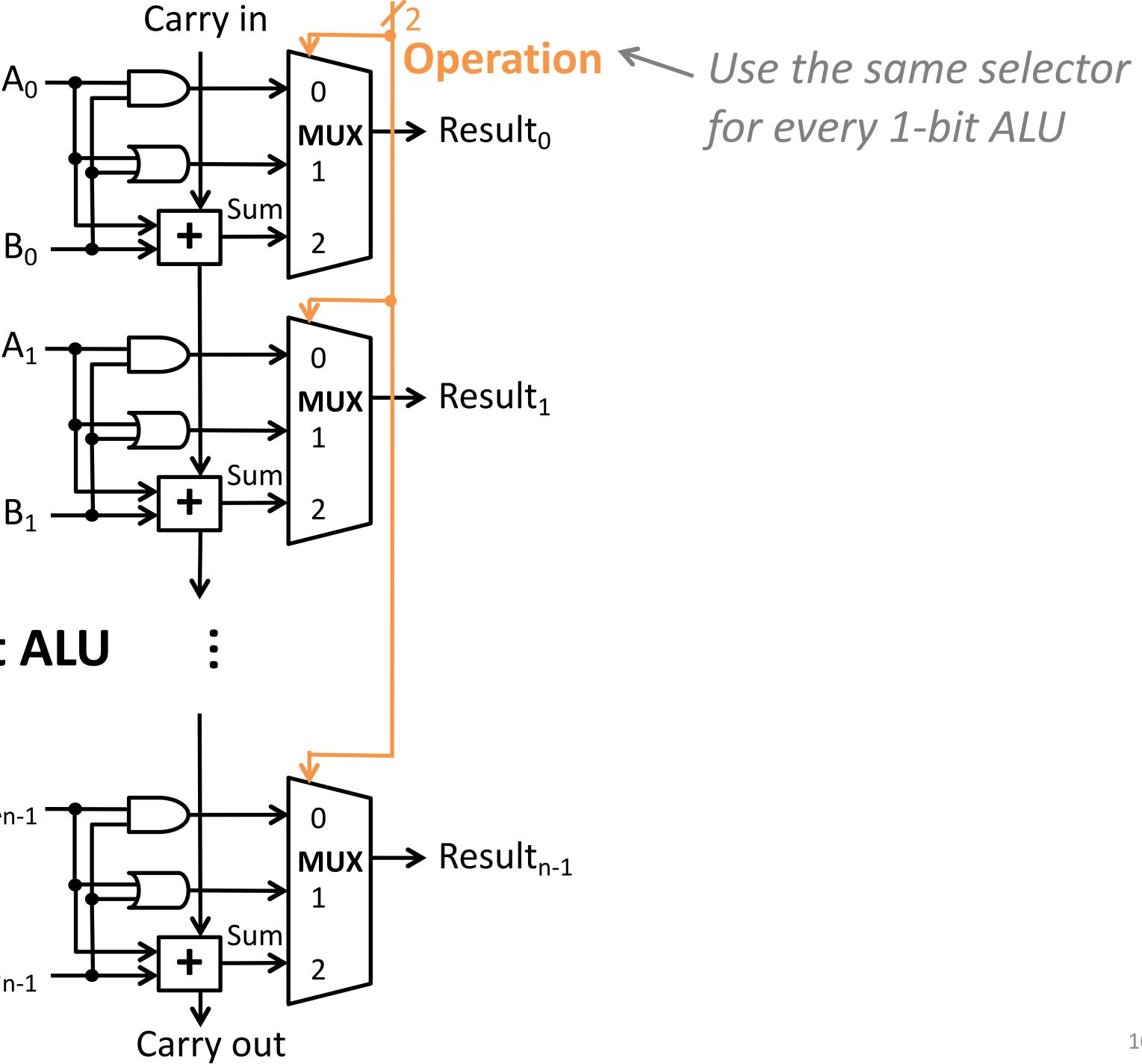

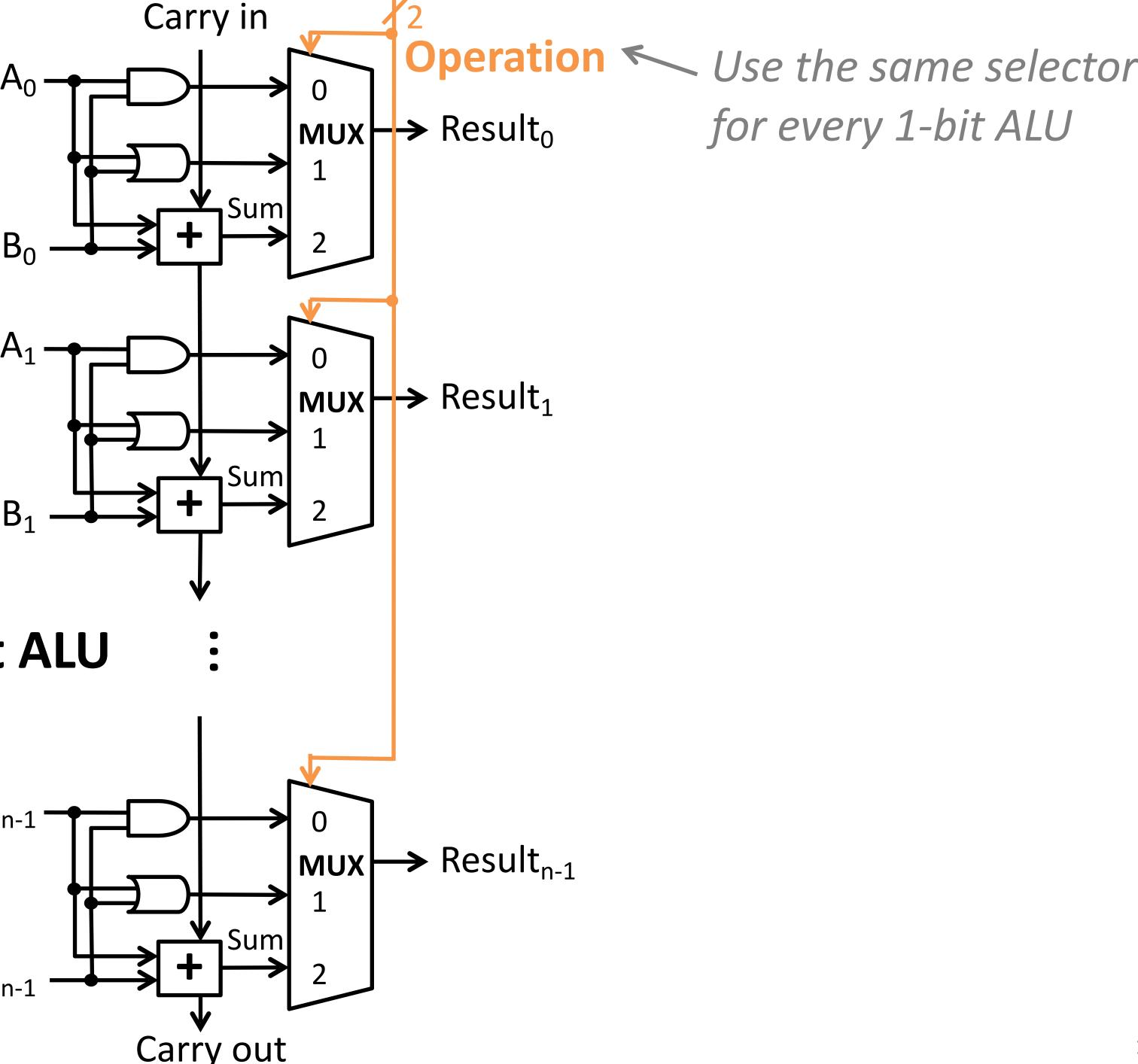

#### We will use *n* 1-bit ALUs to build an n-bit ALU.

Each bit *i* in the result is computed from the corresponding bit *i* in the two inputs.

An example (simplified) 1-bit ALU

Operation

Result

| Ор | Α | B | Result |

|----|---|---|--------|

| 0  | 0 | 0 |        |

| 0  | 0 | 1 |        |

| 0  | 1 | 0 |        |

| 0  | 1 | 1 |        |

| 1  | 0 | 0 |        |

| 1  | 0 | 1 |        |

| 1  | 1 | 0 |        |

| 1  | 1 | 1 |        |

e

### 1-bit ALU: 3 operations

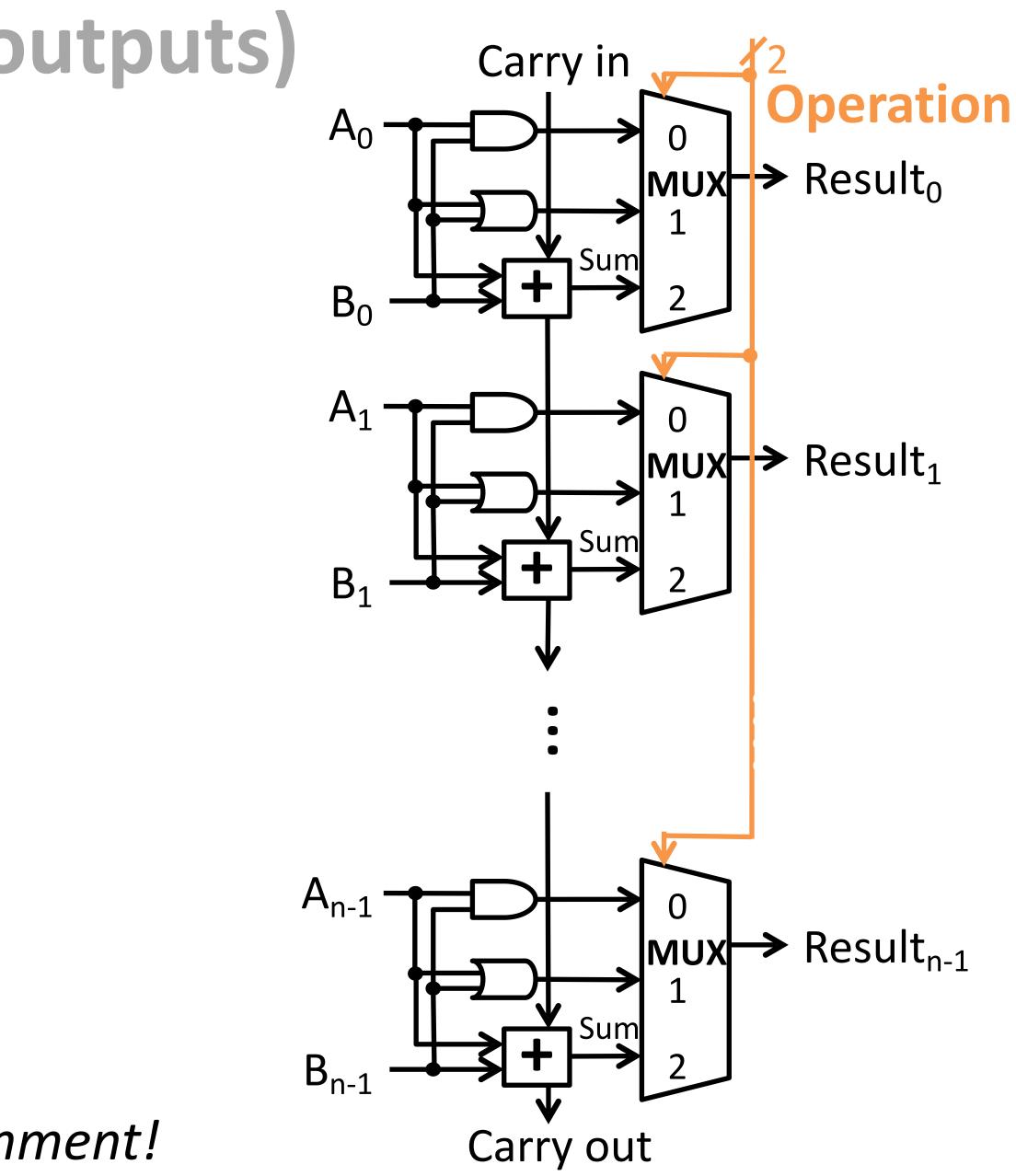

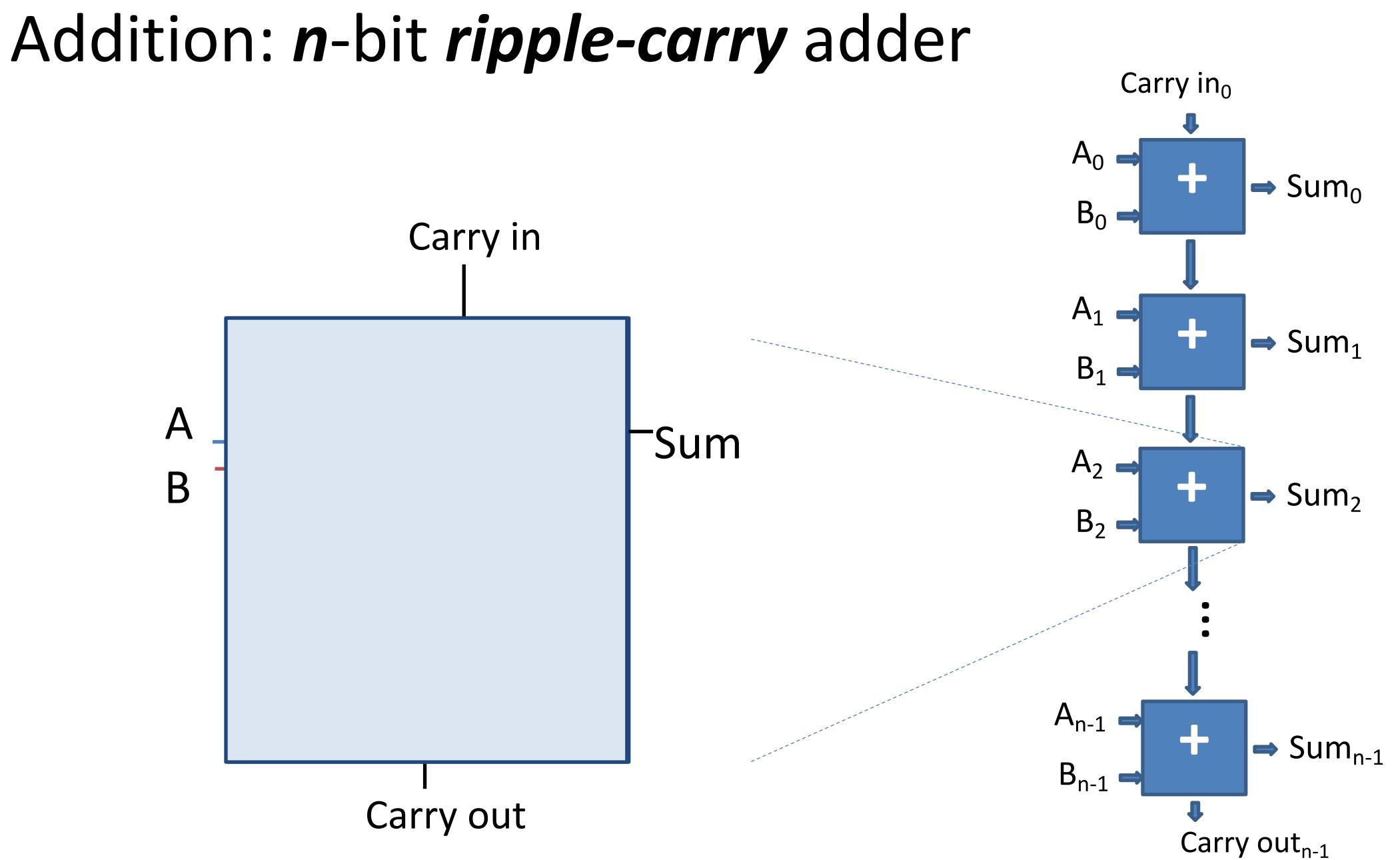

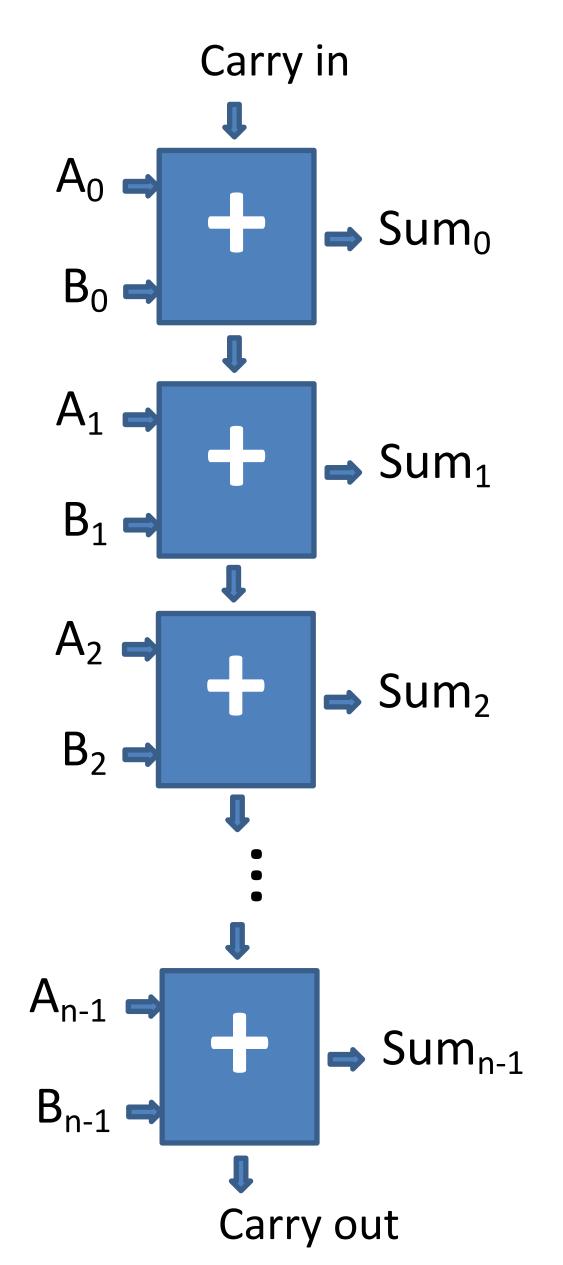

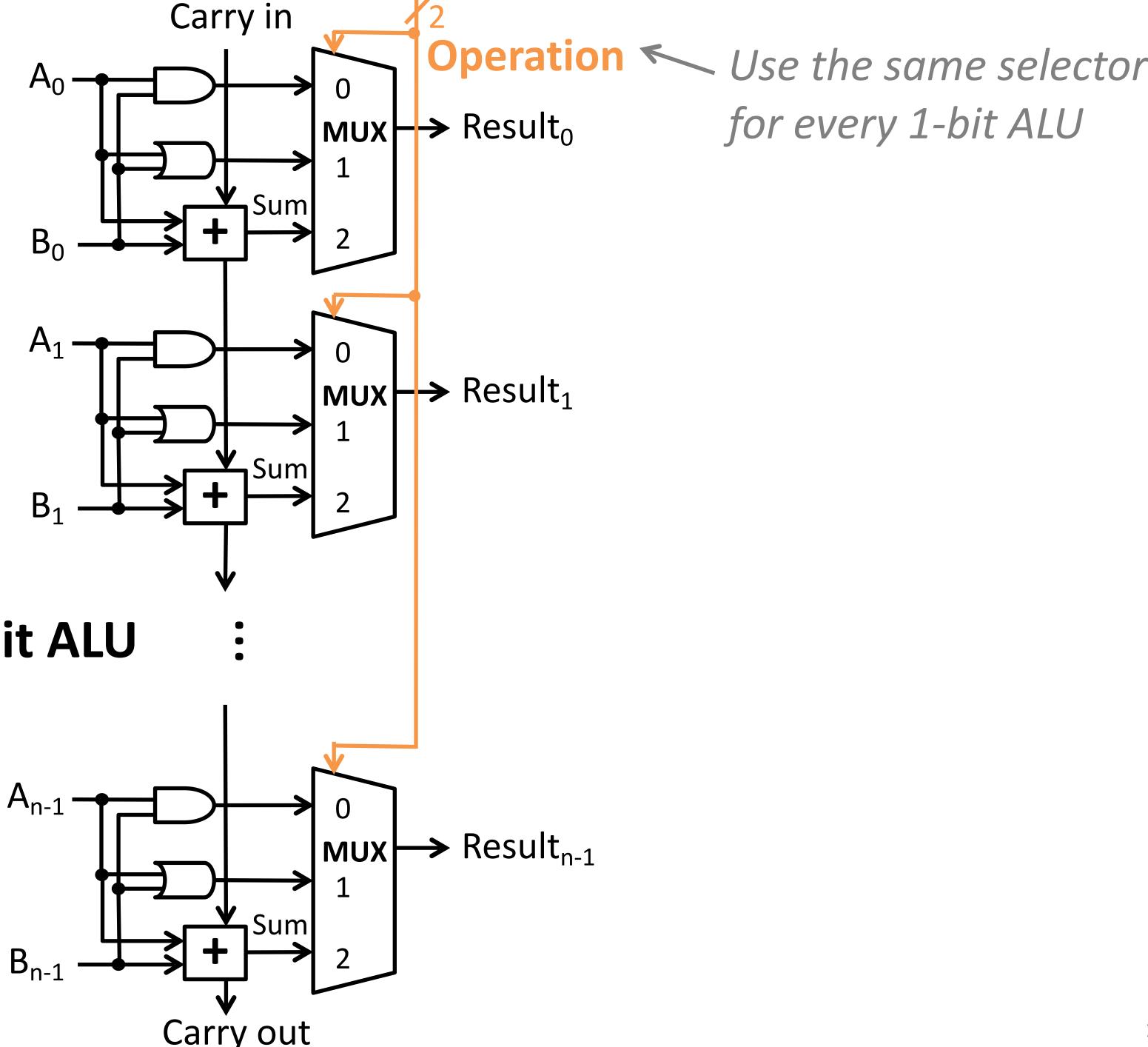

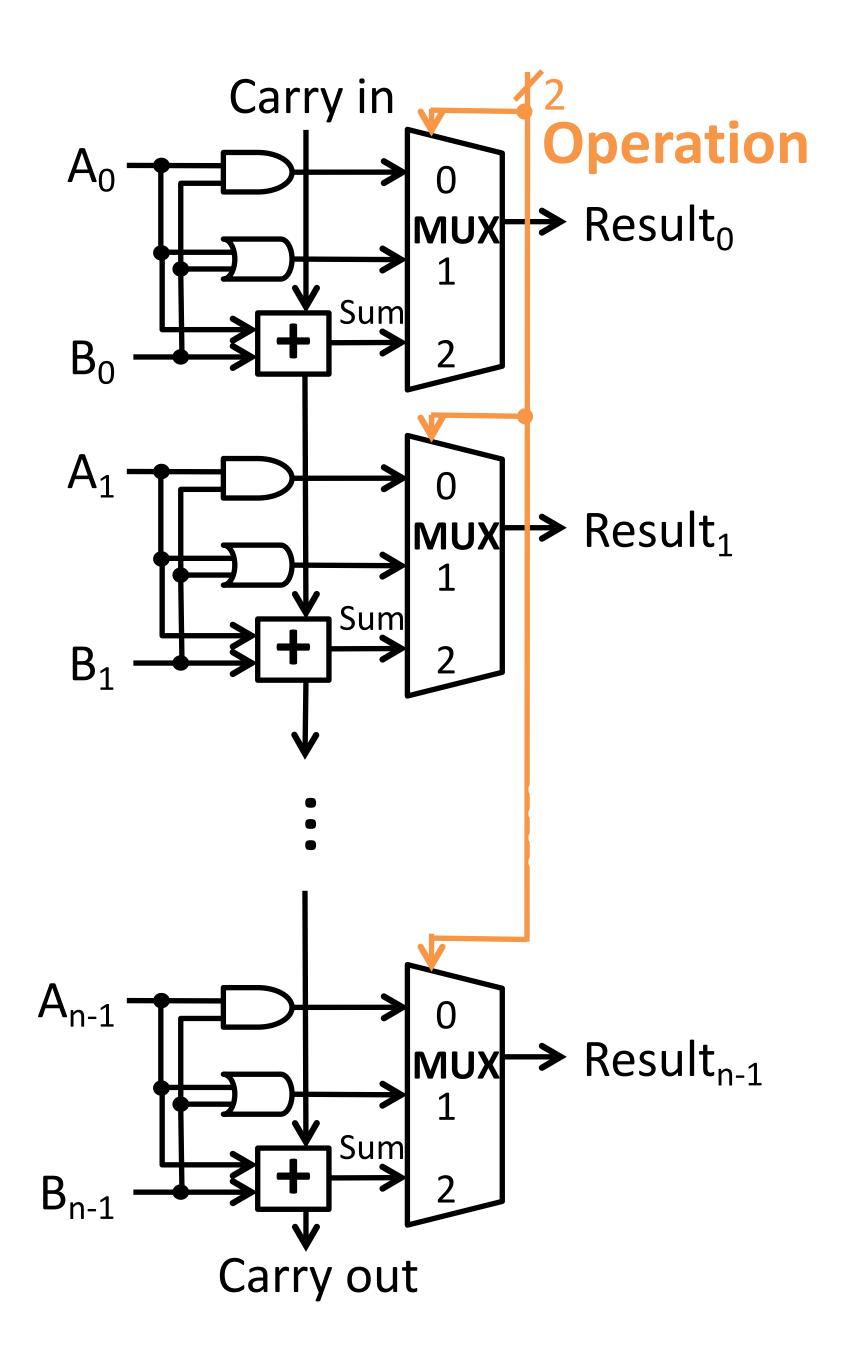

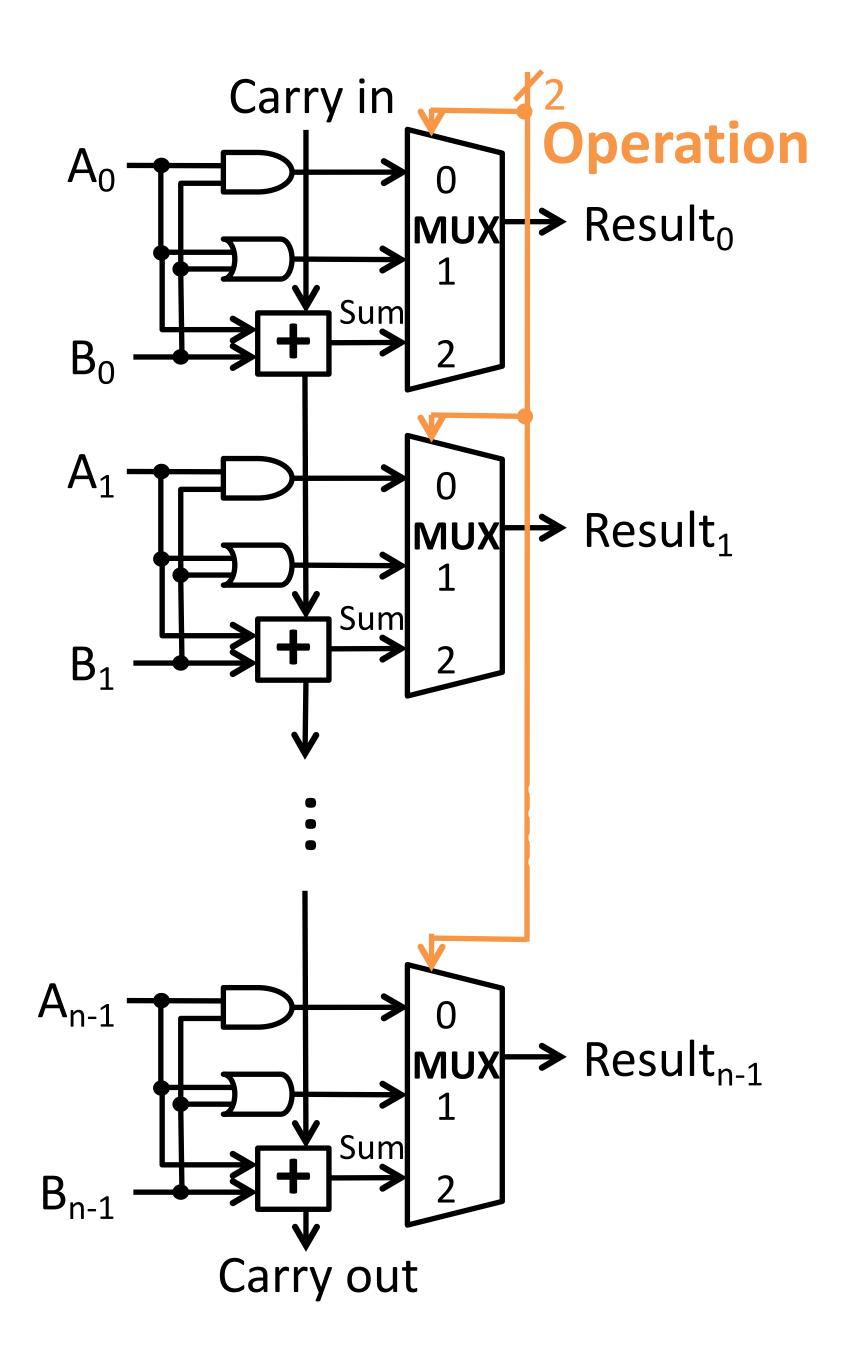

### n-bit ripple carry adder

n-bit ALU

### **Controlling the ALU**

| ALU control lines | Function |

|-------------------|----------|

| 00                | AND      |

| 01                | OR       |

| 10                | add      |

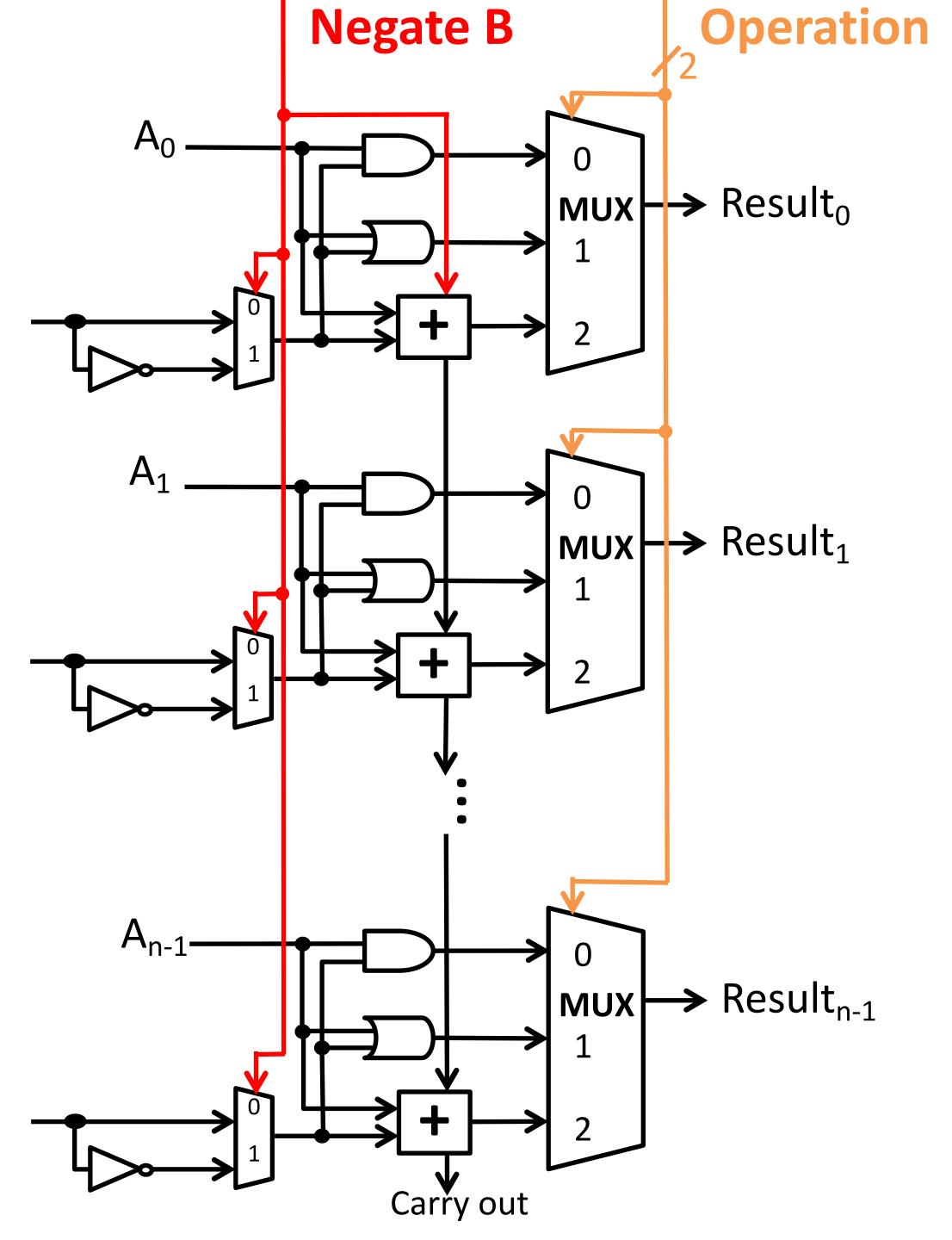

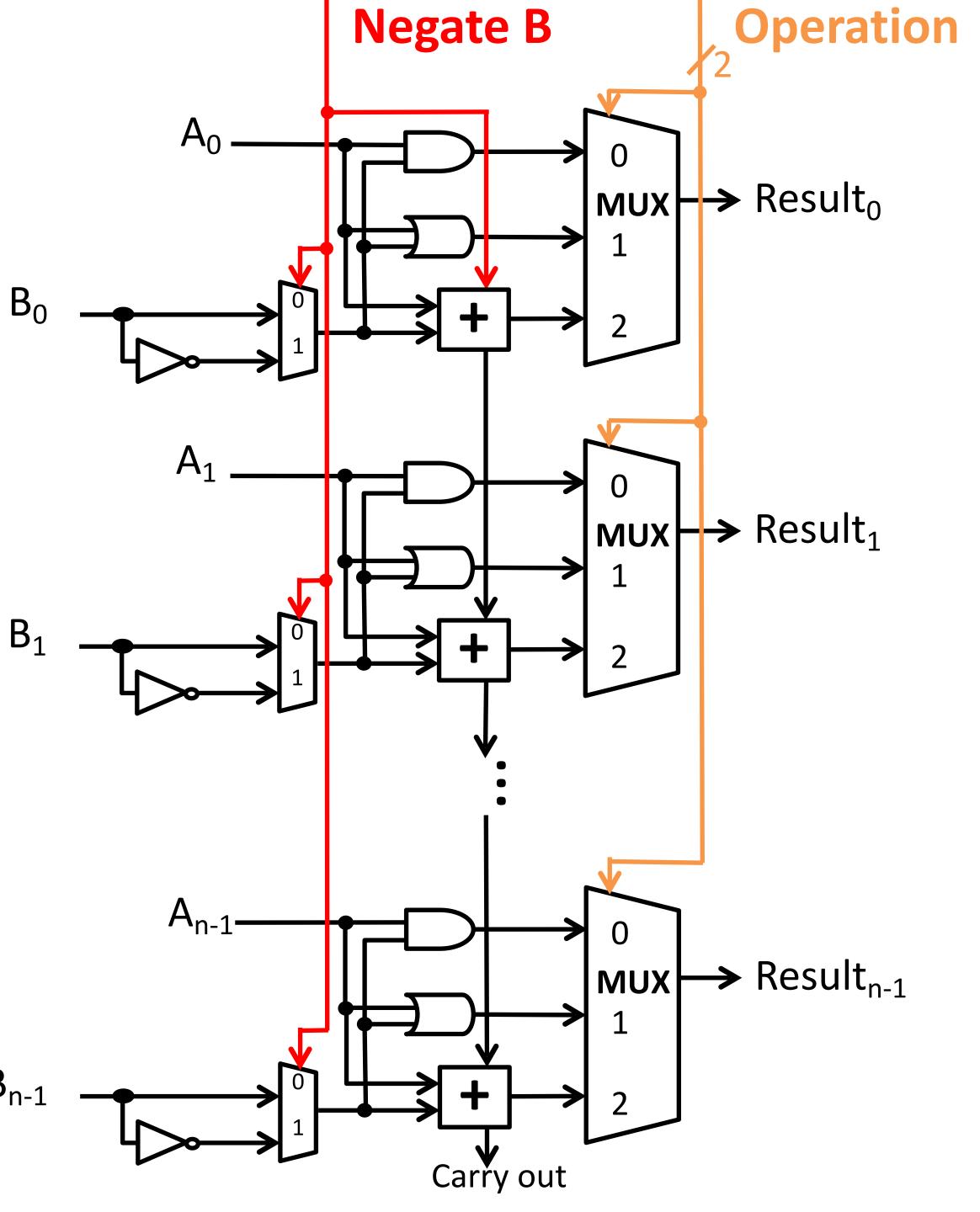

## Include subtraction

How can we control ALU inputs or add minimal new logic to **also compute A–B**?

**Recall:**

A - B = A + (-B)= A + (~B + 1)

#### Plan:

Feed bitwise-not B into the adder Add an extra 1: how?

## Include subtraction

#### Plan to compute A–B:

1. Feed bitwise-not B into the adder  $B_0$ 2. Add an extra 1

### Key insight:

The *same* selector bit (0 or 1) can be used for both!

- Feed the selector into a new 2:1 mux to choose B or ~B

- 2. Feed the selector in as the carry in to the least significant bit

B<sub>n-1</sub>

$B_1$

### **Include** subtraction

| ALU control lines | Function |

|-------------------|----------|

| 000               | AND      |

| 001               | OR       |

| 010               | add      |

| 110               | subtract |

| •••               | •••      |

$A_0$  –

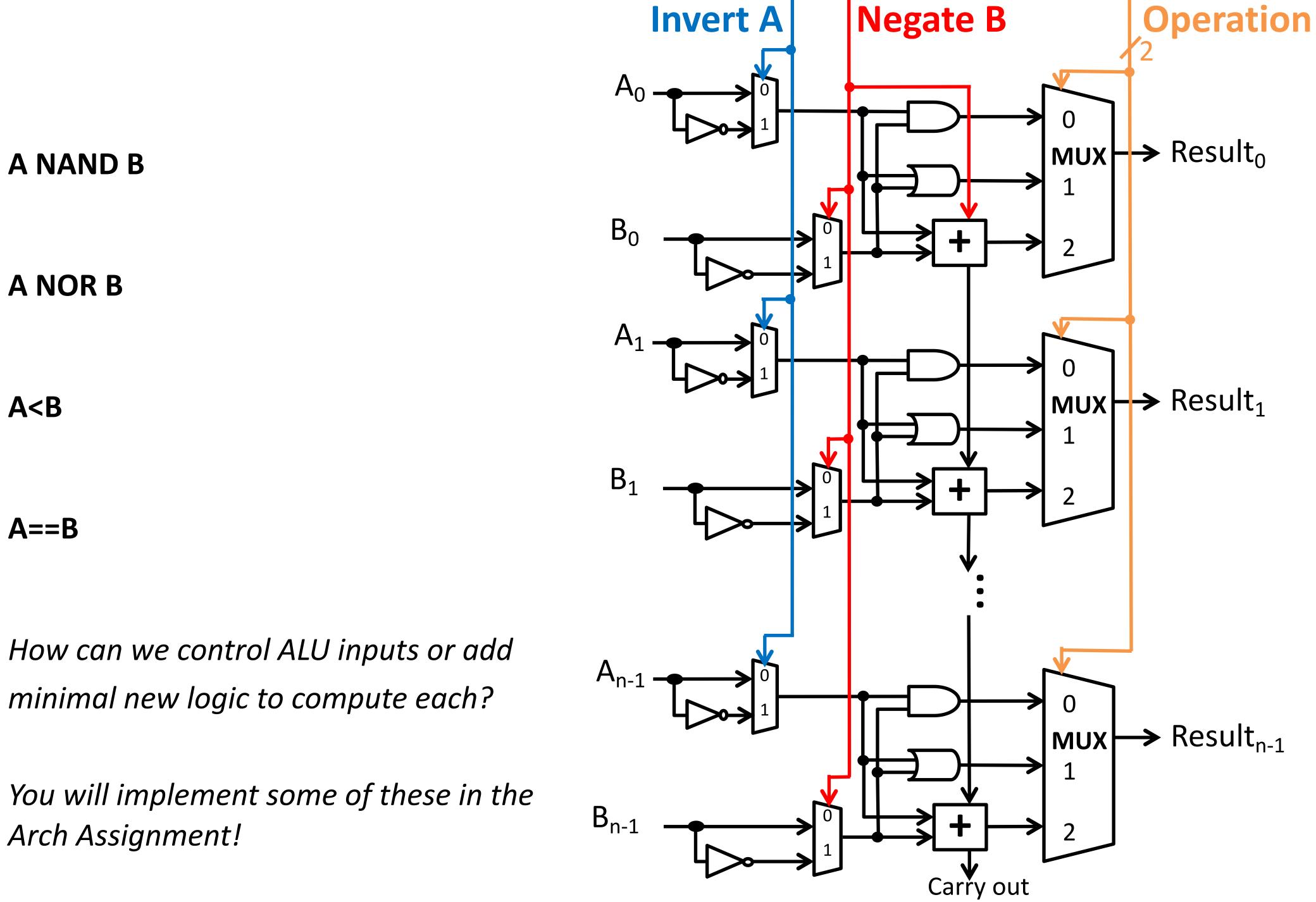

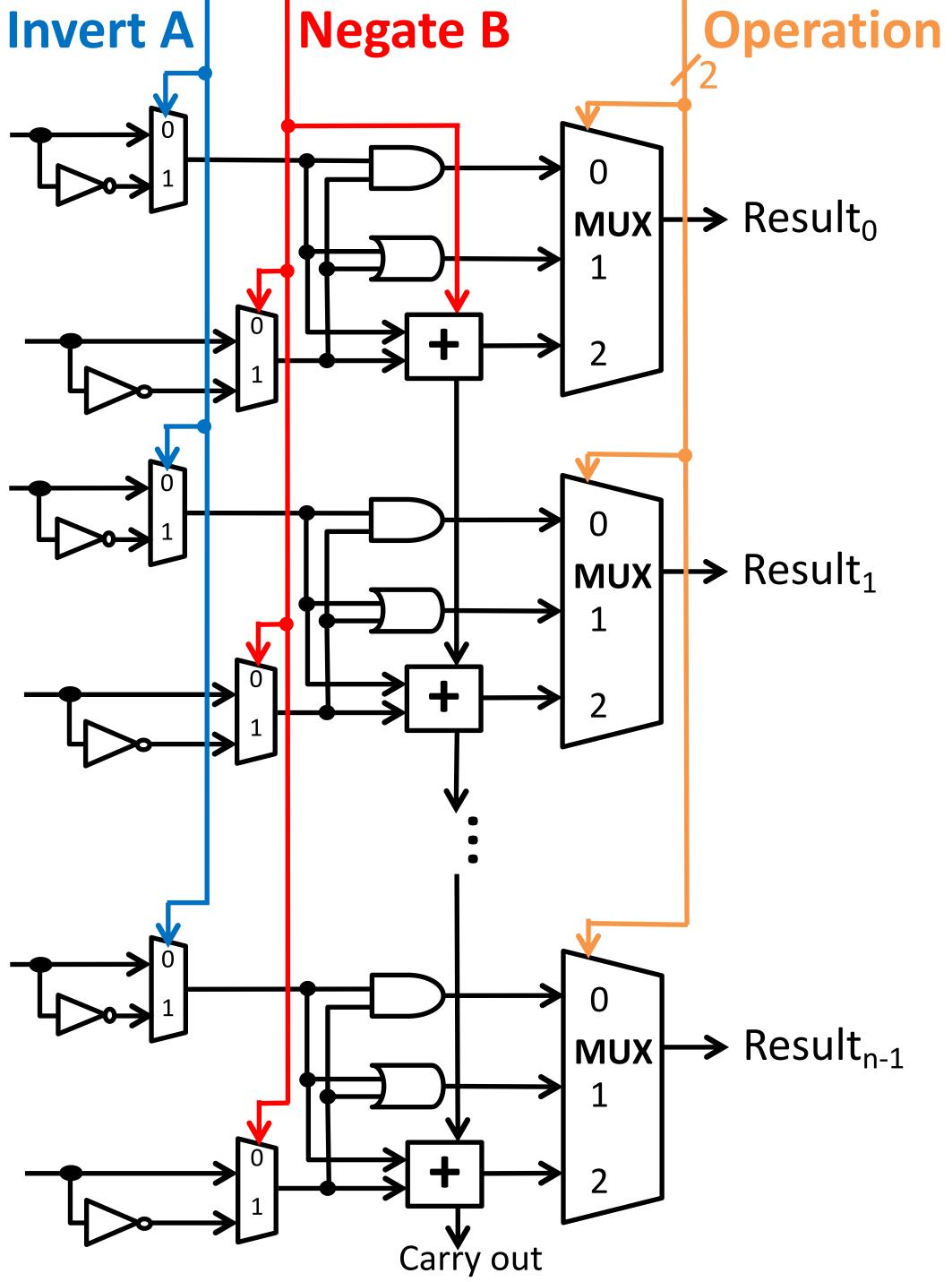

| ALU control lines | Function  |

|-------------------|-----------|

| 0000              | AND       |

| 0001              | OR        |

| 0010              | add       |

| <b>01</b> 10      | subtract  |

| <b>???</b> ?      | NAND      |

| <b>????</b>       | NOR       |

| <b>????</b>       | less than |

| <b>????</b>       | equals    |

$B_0$ A<sub>1</sub> - $B_1$

$B_{n-1}$

$A_{n-1}$

| 10 |

|----|

|----|

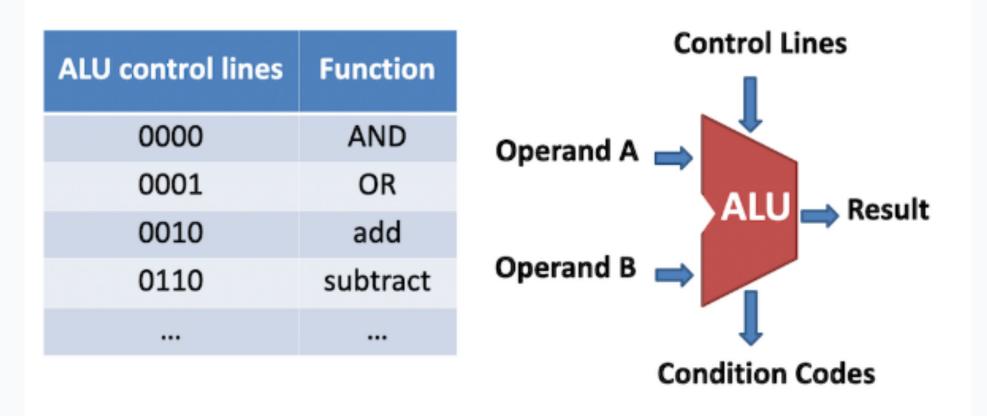

## **Controlling the ALU**

| ALU control lines | Function |

|-------------------|----------|

| 0000              | AND      |

| 0001              | OR       |

| 0010              | add      |

| 0110              | subtract |

|                   | •••      |

# Control Lines Operand A Operand B Condition Codes

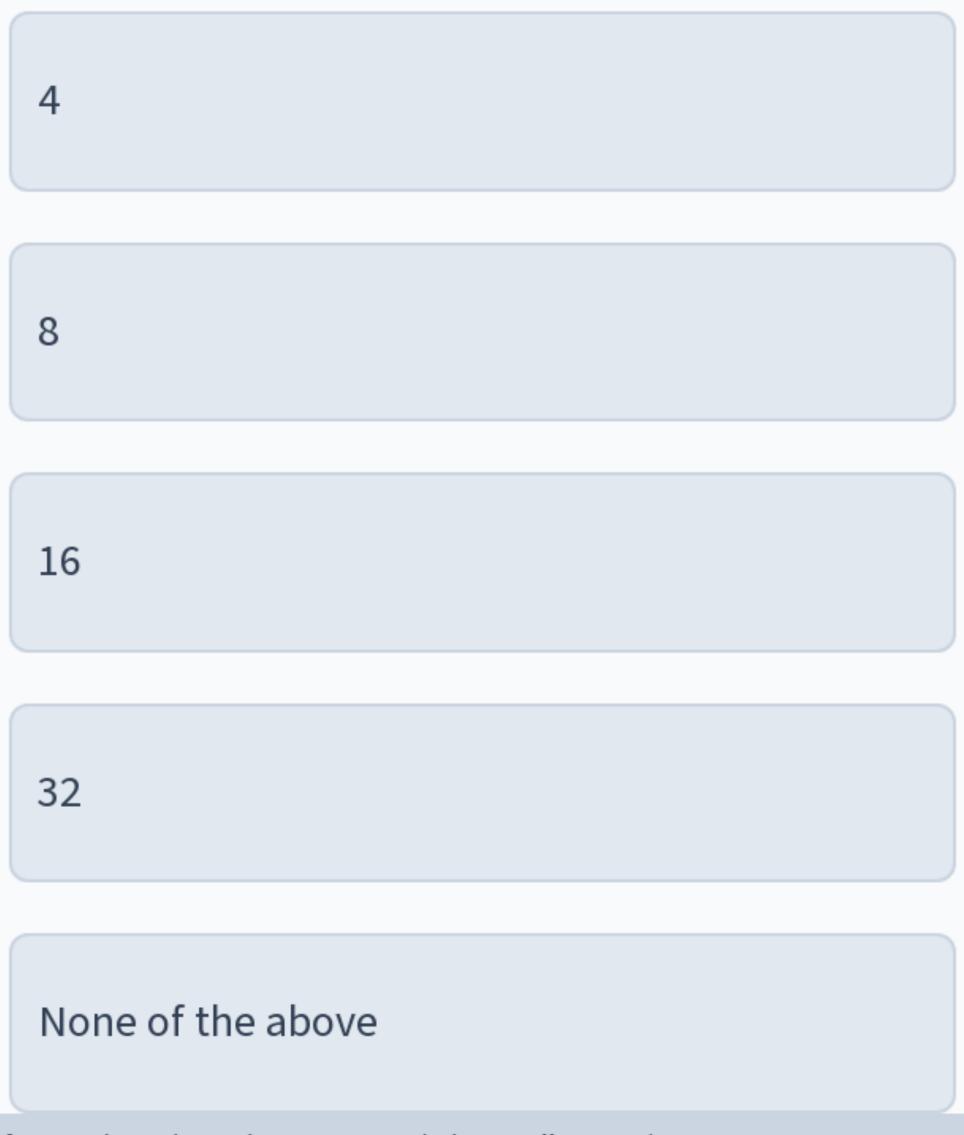

#### How many different functions (operations) could this ALU theoretically perform?

Start the presentation to see live content. For screen share software, share the entire screen. Get help at **pollev.com/app**

#### How many different functions (operations) could this ALU theoretically perform?

Start the presentation to see live content. For screen share software, share the entire screen. Get help at **pollev.com/app**

#### How many different functions (operations) could this ALU theoretically perform?

Start the presentation to see live content. For screen share software, share the entire screen. Get help at **pollev.com/app**

### ALU conditions (additional outputs)

**Extra ALU outputs** describing properties of result.

**Zero Flag:** 1 if result is 00...0 else 0

**Sign Flag:** 1 if result is negative else 0

**Carry Flag:** 1 if carry out else 0

(Signed) **Overflow Flag:** 1 if signed overflow else 0

You will implement these in the Arch Assignment!