## **CS 240 Pensieve Processing**

Name:

About how many hours did you spend actively working on this assignment? \_\_\_\_\_

### 1. Reconstructing Memories

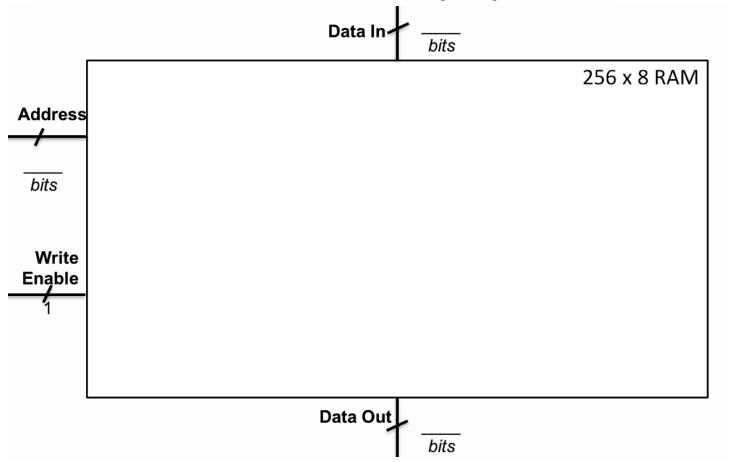

**1a.** Draw a 256×8 RAM based on two 256×4 RAMs. Your logic will go inside the box.

### 2. Taking Control

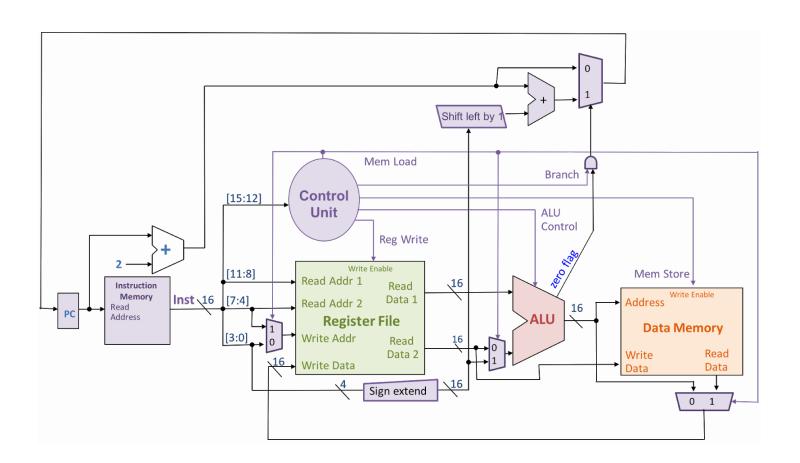

#### **Control Unit Truth Table**

| Instruction<br>Name | Opcode <sub>[3:0]</sub> (4 bits) | Reg Write<br>(1 bit) | ALU Op <sub>[3:0]</sub><br>(4 bits) | Mem Store<br>(1 bit) | Mem Load<br>(1 bit) | Branch<br>(1 bit) | Jump <b>(4a)</b> (1 bit) |

|---------------------|----------------------------------|----------------------|-------------------------------------|----------------------|---------------------|-------------------|--------------------------|

| LW                  |                                  |                      |                                     |                      |                     |                   |                          |

| SW                  |                                  |                      |                                     |                      |                     |                   |                          |

| ADD                 |                                  |                      |                                     |                      |                     |                   |                          |

| SUB                 |                                  |                      |                                     |                      |                     |                   |                          |

| AND                 |                                  |                      |                                     |                      |                     |                   |                          |

| OR                  |                                  |                      |                                     |                      |                     |                   |                          |

| BEQ                 |                                  |                      |                                     |                      |                     |                   |                          |

| JMP (4a)            |                                  |                      |                                     |                      |                     |                   |                          |

| NAND (5b)           |                                  |                      |                                     |                      |                     |                   |                          |

# 3. Jumping into the Unknown

**3a.** Draw JMP logic and fill the JMP row in the control unit truth table above.

| 3b i. Execute this code, assuming R2 holds 5 and R3 holds 2. Indicate the final register values when the code reaches HALT.  0: AND R2, R2, R4 2: AND R3, R3, R5 4: BEQ R5, R0, 3 6: SUB R5, R1, R5 8: ADD R4, R4, R4 A: JMP 2 C: HALT # Stops execution.  R2: R3: R4: R5: |                                                |                   |                  | 3b ii. Single line of C code equivalent to this code.  R4 = |                                             |              |  |             |             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|------------------|-------------------------------------------------------------|---------------------------------------------|--------------|--|-------------|-------------|

| <b>4b-c.</b> NAND/NOT encoding and definition                                                                                                                                                                                                                              |                                                |                   |                  | 16-bit encoding                                             |                                             |              |  |             |             |

| Assembly                                                                                                                                                                                                                                                                   | Meanir                                         | Meaning           |                  | Opcode<br>[15:12]                                           |                                             | Rs<br>[11:8] |  | Rt<br>[7:4] | Rd<br>[3:0] |

| (5b) NAND Rs,Rt,I                                                                                                                                                                                                                                                          | Rd <i>R[d]</i>                                 | R[d] ← ~(Rs & Rt) |                  |                                                             |                                             |              |  |             |             |

| (5c) NOT Rs,Rd                                                                                                                                                                                                                                                             | R[d]                                           | R[d] ← ~Rs        |                  |                                                             |                                             |              |  |             |             |

| 5. Points Affixed and                                                                                                                                                                                                                                                      | 5. Points Affixed and Afloat in a C of Numbers |                   |                  |                                                             |                                             |              |  |             |             |

| 5a. Fixed point numl Sea Type                                                                                                                                                                                                                                              | Minimum<br>(base ten)                          |                   | ximum<br>se ten) | iii. A                                                      | iii. Adder (It fits! Reuse provided parts.) |              |  |             |             |

| i. signed fixed8th                                                                                                                                                                                                                                                         |                                                |                   |                  |                                                             |                                             |              |  |             |             |

| ii.<br>signed fixed32n                                                                                                                                                                                                                                                     |                                                |                   |                  |                                                             |                                             |              |  |             |             |

| <b>5b.</b> Floating point cor                                                                                                                                                                                                                                              | nversion.                                      |                   |                  |                                                             |                                             |              |  |             |             |

| 6-bit floating-point encoding                                                                                                                                                                                                                                              |                                                |                   | 01 0111          |                                                             | 00                                          | 000011       |  | 010010      | 111101      |

| Decimal number represented                                                                                                                                                                                                                                                 |                                                |                   |                  |                                                             |                                             |              |  |             |             |