| HW ISA M: Data Memory                                                                                                                                                                                                         | What is the full word stored at address 0x2?                                                                                                                       | c 🖉 0 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ADSUS<br>We'll think of the data memory like this:                                                                                                                                                                            | 0x2345                                                                                                                                                             |       |

| Memory is byte-addressable, accesses full words (16 bits)       Address       Contents         0x0 - 0x1       0x01       0x00         Memory is "Little Endian": the "little" (low) byte is stored       0x2 - 0x3       0x2 | Address         Contents           0x0 - 0x1         0x01         0x00           0x2 - 0x3         0x23         0x45           0x4 - 0x5         0x67         0xab |       |

| at the lower address.                                                                                                                                                                                                         | 0x6 - 0x7         0x2300           0x8 - 0x9         0x2300           0xA - 0xB         0x2300                                                                     |       |

| Example: storing 1 at address 0x0 yields                                                                                                                                                                                      | 0xC - 0xD 0x0023                                                                                                                                                   |       |

| 11                                                                                                                                                                                                                            | 0x2367 Start the presentation to see live content. For screen share software, share the entire screen. Get help at pollex.com/app                                  |       |

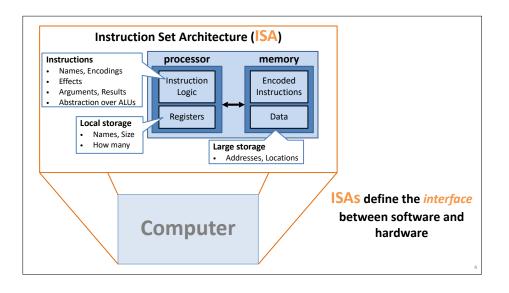

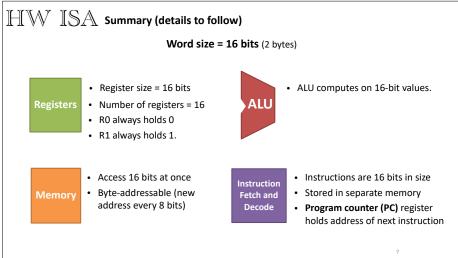

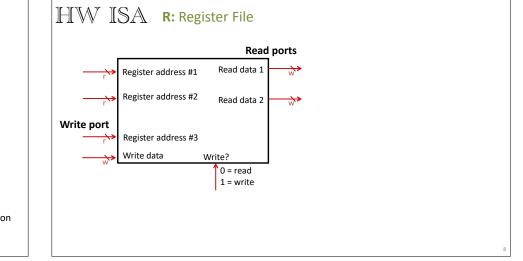

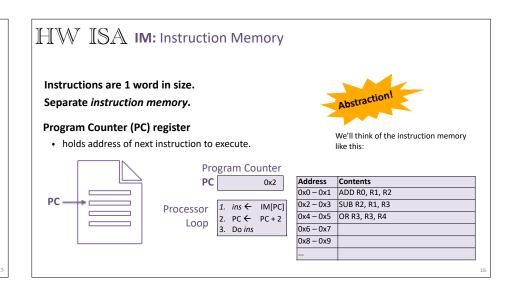

| HW 2                               | ISA Instru                 | uctions                                                     | <sub>MSB</sub> 16 | 5-bit E | ncodi | ng <sub>LSB</sub> |              |

|------------------------------------|----------------------------|-------------------------------------------------------------|-------------------|---------|-------|-------------------|--------------|

|                                    | Assembly Syntax            | (R = register file,<br>Meaning M = data memory)             | Opcode            | Rs      | Rt    | Rd                |              |

|                                    | ADD Rs, Rt, Rd             | $R[d] \leftarrow R[s] + R[t]$                               | 0010              | 5       | t     | d                 |              |

|                                    | SUB Rs, Rt, Rd             | $R[d] \leftarrow R[s] - R[t]$                               | 0011              | 5       | t     | d                 | - Arithmetic |

|                                    | AND Rs, Rt, Rd             | $R[d] \leftarrow R[s] \& R[t]$                              | 0100              | 5       | t     | d                 | Antimetic    |

|                                    | OR Rs, Rt, Rd              | $R[d] \leftarrow R[s] \mid R[t]$                            | 0101              | 5       | t     | d                 |              |

|                                    | LW R <i>t, offset</i> (Rs) | $R[t] \leftarrow M[R[s] + offset]$                          | 0000              | 5       | t     | offset            | Memory       |

|                                    | SW Rt, offset(Rs)          | $M[R[s] + offset] \leftarrow R[t]$                          | 0001              | 5       | t     | offset            | - Memory     |

|                                    | BEQ Rs, Rt, offset         | If $R[s] == R[t]$ then<br>PC $\leftarrow$ PC + 2 + offset*2 | 0111              | 5       | t     | offset            | Control flov |

| MP offset is<br>unsigned           | JMP offset                 | PC ← offset*2                                               | 1000              |         | offse | t                 |              |

| other offsets<br>are <i>signed</i> | HALT                       | Stops program execution                                     | 1111              |         |       |                   | -            |

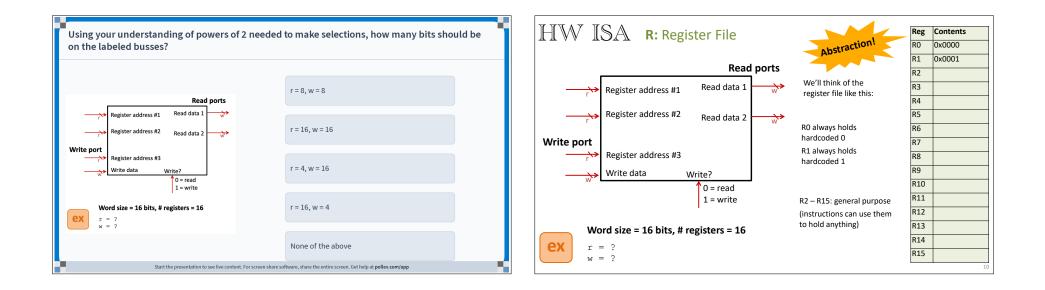

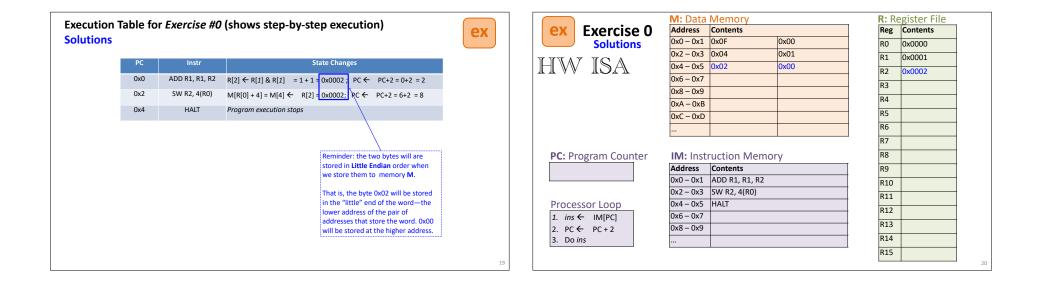

| What is the next operation this processor will do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ?                                                                    | Ø0 8            | Exercise 0                                                                   | Address                                                                                 | Memory<br>Contents                                |           |                                  | egister File<br>Contents |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------|-----------|----------------------------------|--------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ADD                                                                  | Fill i<br>mac   | N ISA<br>n the rest of the<br>thine state based on<br>initial state          | 0x0 - 0x1<br>0x2 - 0x3<br>0x4 - 0x5<br>0x6 - 0x7<br>0x8 - 0x9<br>0xA - 0xB<br>0xC - 0xD |                                                   | 0x00 0x01 | R0<br>R1<br>R2<br>R3<br>R4<br>R5 | 0x0000 0x0001            |

| Program Counter<br>PC         0.2         Adfress<br>0x2-0x1         Contents<br>0x2-0x1         SUB         SUB           Processor<br>Loop         1. im < Mil(ret)<br>3. bo im         0x2-0x1         0x8.78, 18, 18         0x2-0x1         0x2-0x | SUB                                                                  |                 | Program Counter                                                              | <br>IM: Inst                                                                            | ruction Memo                                      | ry        | R6<br>R7<br>R8                   |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OR                                                                   |                 |                                                                              | Address<br>0x0 - 0x1<br>0x2 - 0x3                                                       | <b>Contents</b><br>ADD R1, R1, R2<br>SW R2, 4(R0) |           | R9<br>R10<br>R11                 |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | None of the above                                                    | <i>1.</i><br>2. | becessor Loop<br>ins $\leftarrow$ IM[PC]<br>PC $\leftarrow$ PC + 2<br>Do ins | 0x4 - 0x5<br>0x6 - 0x7<br>0x8 - 0x9<br>                                                 |                                                   |           | R12<br>R13<br>R14<br>R15         |                          |

| Start the presentation to see live content. For screen share                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | software, share the entire screen. Get help at <b>pollev.com/app</b> |                 |                                                                              |                                                                                         |                                                   |           |                                  |                          |

| × Exercise 1           | Address                        | Memory<br>Contents |      | Reg | Contents |

|------------------------|--------------------------------|--------------------|------|-----|----------|

| <pre>LYELCISE T</pre>  | 0x0 - 0x1                      |                    | 0x00 | RO  | 0x0000   |

|                        | 0x0 - 0x1<br>0x2 - 0x3         |                    | 0x01 |     |          |

| N ISA                  | $0x^2 = 0x^3$<br>$0x^4 - 0x^5$ | 0,04               | 0,01 | R1  | 0x0001   |

| V IOLI                 |                                |                    |      | R2  |          |

|                        | 0x6 – 0x7                      |                    |      | R3  |          |

| n the rest of the      | 0x8 – 0x9                      |                    |      | R4  |          |

| chine state based on   | 0xA – 0xB                      |                    |      |     |          |

| initial state          | 0xC – 0xD                      |                    |      | R5  |          |

| Initial State          |                                |                    |      | R6  |          |

|                        |                                | 1                  |      | R7  |          |

| Program Counter        | IM: Inst                       | ruction Mem        | ory  | R8  |          |

|                        | Address                        | Contents           |      | R9  |          |

|                        | 0x0-0x1                        | LW R3, 0(R0)       |      | R10 |          |

|                        | 0x2 – 0x3                      | LW R4, 2(R0)       |      | R11 |          |

| cessor Loop            | 0x4 – 0x5                      | AND R3, R4, R5     |      |     |          |

| ins ← IM[PC]           | 0x6 – 0x7                      | SW R5, 4(R0)       |      | R12 |          |

| $PC \leftarrow PC + 2$ | 0x8 – 0x9                      | HALT               |      | R13 |          |

| Do ins                 |                                |                    |      | R14 |          |

|                        | -                              | 1                  |      | R15 | -        |

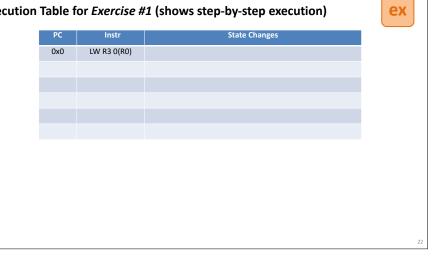

### Execution Table for *Exercise #1* (shows step-by-step execution)

|                         | M: Data   | Memor     | Ņ      | <b>R:</b> R | egister File                    |  |

|-------------------------|-----------|-----------|--------|-------------|---------------------------------|--|

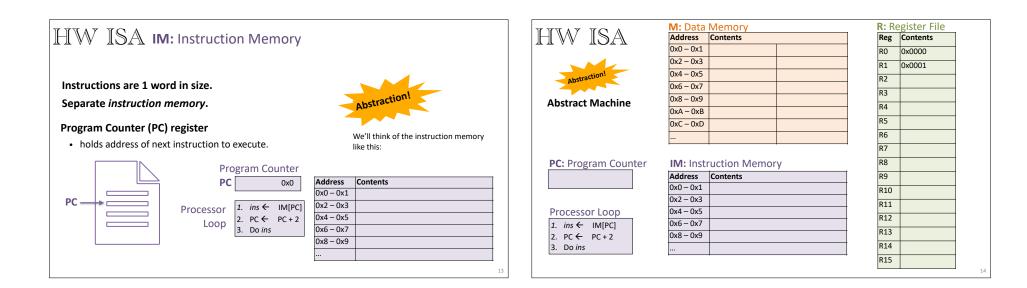

| <b>ex</b> Exercise 2    | Address   | Contents  |        | Reg         | Contents (time: $\rightarrow$ ) |  |

|                         | 0x0 - 0x1 | 0x0F      | 0x00   | RO          | 0x0000                          |  |

|                         | 0x2 – 0x3 | 0x04      | 0x01   | R1          | 0x0001                          |  |

| HW ISA                  | 0x4 – 0x5 |           |        |             | 0,0001                          |  |

|                         | 0x6 – 0x7 |           |        | R2          |                                 |  |

|                         | 0x8 – 0x9 |           |        | R3          |                                 |  |

| Fill in the rest of the | 0xA – 0xB |           |        | R4          |                                 |  |

| machine state based on  | 0xC – 0xD |           |        | R5          |                                 |  |

| this initial state      |           |           |        | R6          |                                 |  |

|                         |           |           |        | R7          |                                 |  |

| PC: Program Counter     | IM: Inst  | ruction   | Memory | R8          |                                 |  |

|                         | Address   | Contents  |        | R9          | 0x0002                          |  |

|                         | 0x0-0x1   | SUB R8, R | 18, R8 | R10         | 0x0003                          |  |

|                         | 0x2 – 0x3 | BEQ R9, F | 10, 3  |             | 0,0003                          |  |

| Processor Loop          | 0x4 – 0x5 | ADD R10,  | R8, R8 | R11         |                                 |  |

| 1. ins ← IM[PC]         | 0x6 – 0x7 | SUB R9, R | 1, R9  | R12         |                                 |  |

| 2. PC ← PC + 2          | 0x8 – 0x9 | JMP 1     |        | R13         |                                 |  |

| 3. Do ins               | 0xA – 0xB | HALT      |        | R14         |                                 |  |

|                         |           |           |        | R15         |                                 |  |

| cution | Table | for Exercise   | #2 (shows step-by-step execution) | ех |

|--------|-------|----------------|-----------------------------------|----|

|        | РС    | Instr          | State Changes                     |    |

| Ĩ      | 0x0   | SUB R8, R8, R8 |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

|        |       |                |                                   |    |

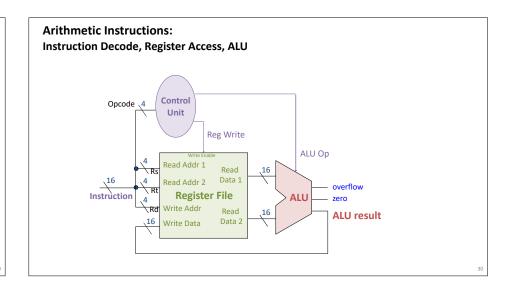

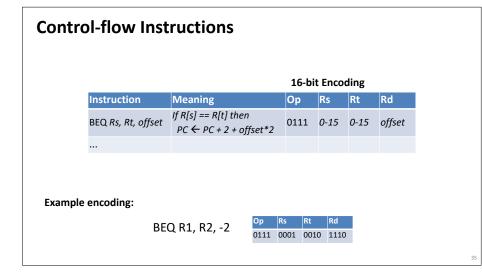

|                       |                                | 16-bi            | t Encod      | ling |      |

|-----------------------|--------------------------------|------------------|--------------|------|------|

| Instruction           | Meaning                        | Opcode           | Rs           | Rt   | Rd   |

| ADD Rs, Rt, Rd        | $R[d] \leftarrow R[s] + R[t]$  | 0010             | 0-15         | 0-15 | 0-15 |

| SUB <i>Rs, Rt, Rd</i> | $R[d] \leftarrow R[s] - R[t]$  | 0011             | 0-15         | 0-15 | 0-15 |

| AND <i>Rs, Rt, Rd</i> | $R[d] \leftarrow R[s] \& R[t]$ | 0100             | 0-15         | 0-15 | 0-15 |

| OR <i>Rs, Rt, Rd</i>  | $Rd \leftarrow R[s] \mid R[t]$ | 0101             | 0-15         | 0-15 | 0-15 |

|                       |                                |                  |              |      |      |

| e encoding:<br>ADD F  | R3, R6, R8 0pcode<br>0010      | Rs Rt<br>0011 01 | Rd<br>10 100 | 0    |      |

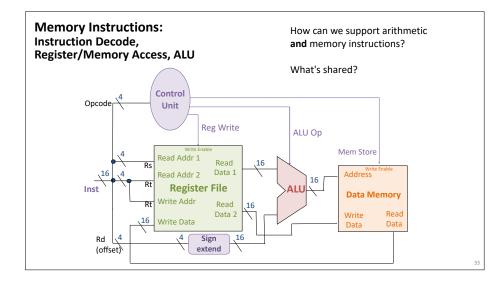

| Me   | mory Instru          | ctions                               |        |      |      |        |  |

|------|----------------------|--------------------------------------|--------|------|------|--------|--|

|      | Instruction          | Meaning                              | Ор     | Rs   | Rt   | Rd     |  |

|      | LW Rt, offset(Rs)    | $R[t] \leftarrow Mem[R[s] + offset]$ | 0000   | 0-15 | 0-15 | offset |  |

|      | SW Rt, offset(Rs)    | $Mem[R[s] + offset] \leftarrow R[t]$ | 0001   | 0-15 | 0-15 | offset |  |

|      |                      |                                      |        |      |      |        |  |

| Exai | mple encoding:<br>SW | R6, -8(R3) Opcode Rs<br>0001 001     | Rt     | Rd   |      |        |  |

|      |                      | 0001 001.                            | 1 0110 | 1000 |      |        |  |

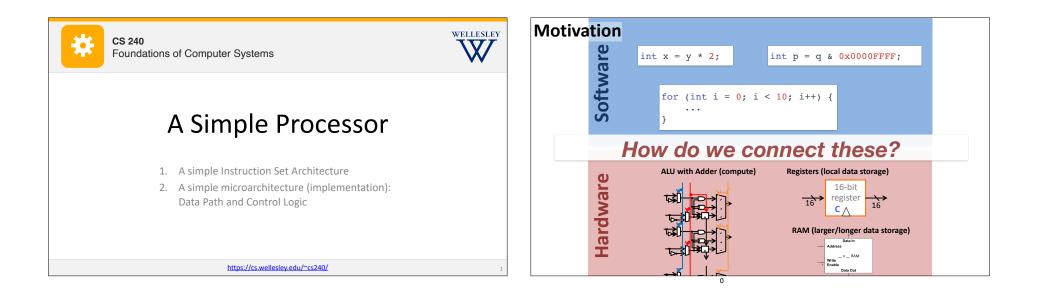

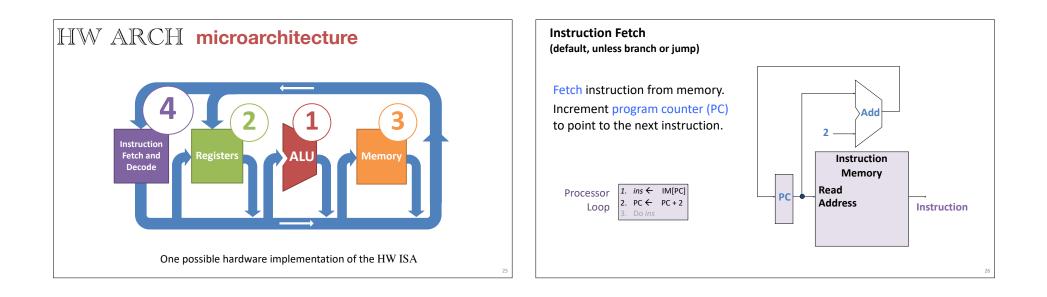

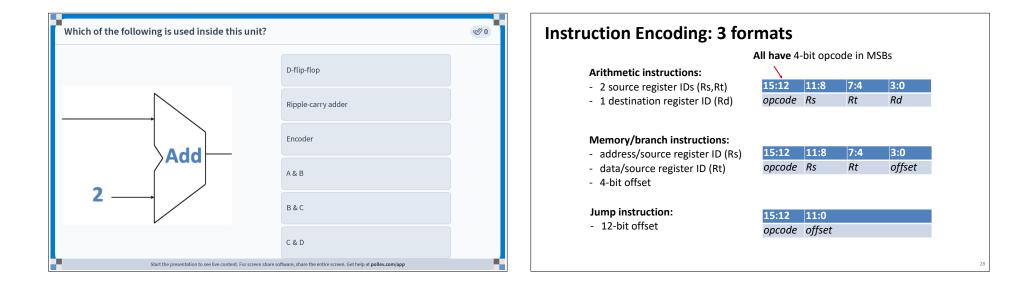

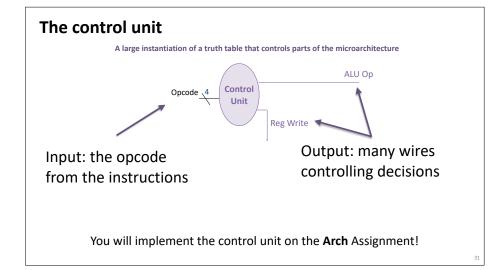

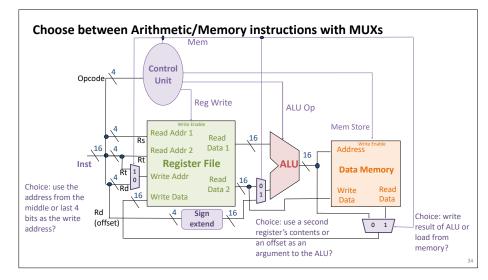

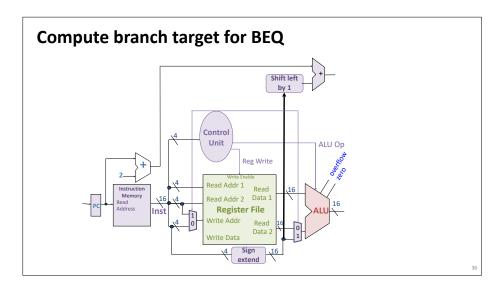

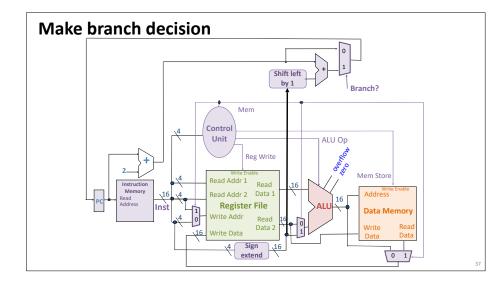

### What's missing from what we covered in lecture?

- Details of Control Unit

- ALU op is not instruction opcode; some translation needed

- Reg Write bit (for ADD, SUB, AND, OR, LW)

- Mem Store bit (for SW)

- Mem bit (arithmetic/memory MUX bit)

- Branch bit (for BEQ)

- Implementation of JMP

- Implementation of HALT (basically stops the clock running the computer; we won't implement this)

See Arch Assignment!

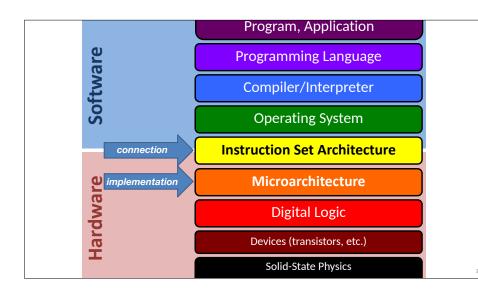

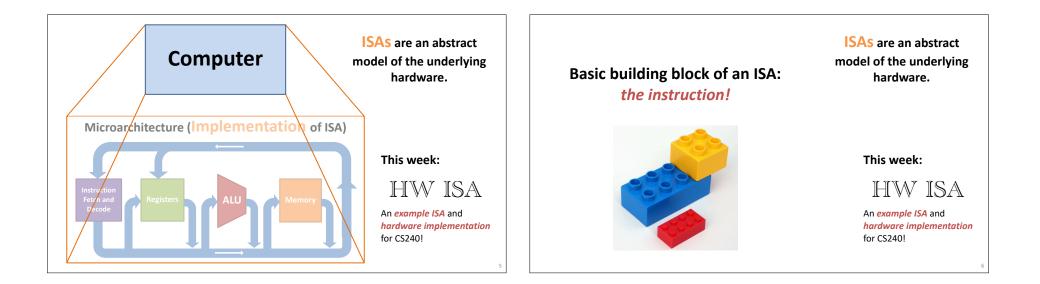

# $HW \ ARCH$ not the only implementation

### Single-cycle architecture

- Relatively simple, (barely!) fits on a slide (and in our heads).

- Every instruction takes one clock cycle each.

- Slowest instruction determines minimum clock cycle.

- Inefficient.

### Could it be better?

- Performance, energy, debugging, security, reconfigurability, ...

- Pipelining

- OoO: Out-of-order execution

- Caching

- ... enormous, interesting design space of Computer Architecture

## **Conclusion of unit: Computational Building Blocks (HW)**

### Lectures

Digital Logic Data as Bits Integer Representation Combinational Logic Arithmetic Logic Sequential Logic A Simple Processor

#### Labs

- 1: Transistors to Gates 2: Data as Bits

- 3: Combinational Logic & Arithmetic 4: ALU & Sequential Logic

- 5: Processor Datapath (next week)

### Topics

Transistors, digital logic gates Data representation with bits, bit-level computation Number representations, arithmetic Combinational and arithmetic logic Sequential (stateful) logic Computer processor architecture overview

#### Assignments

Gates

Zero

Bits

Mid-semester exam 1: HW October 10

Arch (out now!)