## **Computer Science 240**

Assignment for Lab 7

NOTE: You should not try to do the problems on flip-flops until after lecture on Friday.

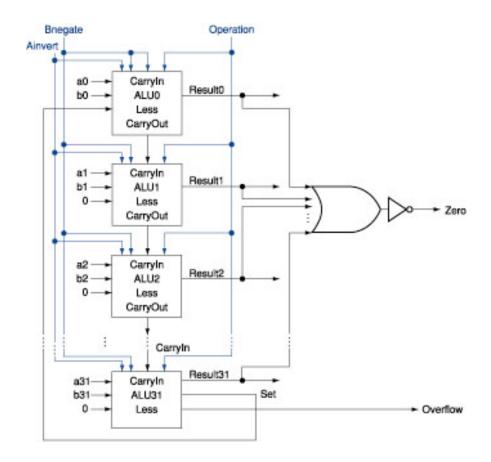

1. Given the following diagram for the ALU, and assuming A and B are 4-bit hexadecimal values, fill the table below:

| Function | <b>Test Inputs</b> | Output | Carry-out | Zero | Overflow |

|----------|--------------------|--------|-----------|------|----------|

| A + B    | A = 3, B = 7       |        |           |      |          |

| A + B    | A = F, B = E       |        |           |      |          |

| A AND B  | A = 1, B = F       |        |           |      |          |

| A AND B  | A = 7, B = 8       |        |           |      |          |

| A OR B   | A = 3, $B = C$     |        |           |      |          |

| A NOR B  | A = 6, B = 9       |        |           |      |          |

| SLT      | A = 3, B = 9       |        |           |      |          |

| SLT      | A = C, B = 7       |        |           |      |          |

- 2. Assume you have an SR latch, S=0 and R=0. Do you know if the output Q is 0 or 1? Explain.

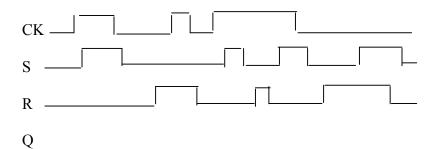

- 3. Assume you have a clocked SR latch. Draw Q, given the following CK, S, and R:

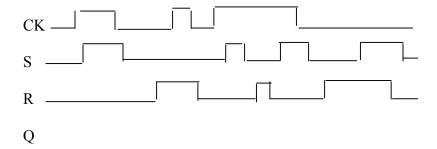

4. Assume you have a clocked SR **flip-flop**, that is activated on the positive edge of the clock. Draw Q given the same CK, S, and R:

5. Explain why your outputs are different for the latch and the flip-flop: