# **Basic building blocks**

Common combinational circuits: encoders, decoders, multiplexers

# Recall: sum of products

logical sum (OR)

of products (AND)

of inputs or their complements (NOT).

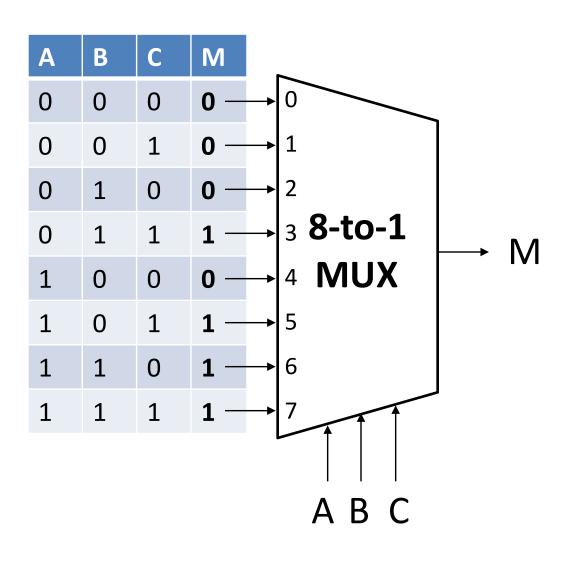

| Α | В | С | M |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

#### Construct with:

- 1 code detector per 1-valued output row

- 1 large OR of all code detector outputs

Is it minimal?

## **Gray Codes = reflected binary codes**

Alternate binary encoding designed for electromechanical switches and counting.

How many bits change when incrementing?

### Karnaugh Maps: find minimal sums of products

|   |   |   |   |            | gray               | code     |             | C         | D         |         |   |

|---|---|---|---|------------|--------------------|----------|-------------|-----------|-----------|---------|---|

| A | В | C | D | F(A, B, C, |                    | der ¯    | <b>→</b> 00 | 01        | 11        | 10      |   |

| 0 | 0 | 0 | 0 | 0          | •                  | Ψ        |             |           |           |         |   |

| 0 | 0 | 0 | 1 | 0          |                    | 00       | 0           | 0         | 0         | 0       |   |

| 0 | 0 | 1 | 0 | 0          |                    |          |             |           |           |         |   |

| 0 | 0 | 1 | 1 | 0          |                    | 01       | 0           | 0         | 0         | 1       |   |

| 0 | 1 | 0 | 0 | 0          | AB                 |          |             |           |           |         |   |

| 0 | 1 | 0 | 1 | 0          |                    | 11       | 1           | 1         | 0         | 1       |   |

| 0 | 1 | 1 | 0 | 1          |                    |          |             |           |           |         |   |

| 0 | 1 | 1 | 1 | 0          |                    | 10       | 1           | 1         | 1         | 1       |   |

| 1 | 0 | 0 | 0 | 1          |                    |          |             |           |           |         |   |

| 1 | 0 | 0 | 1 | 1 1        | . Cover exactly tl | ne 1s b  | y drawir    | ng maxi   | mally si  | zed     |   |

| 1 | 0 | 1 | 0 | 1          | rectangles who     | se dim   | ensions     | (in cells | s) are po | owers o | f |

| 1 | 0 | 1 | 1 | 1          | (They may over     | lap or v | wrap ar     | ound!)    |           |         |   |

- of 2.

- 2. For each rectangle, make a *product* of the inputs (or complements) that are 1 for all cells in the rectangle. (minterms)

- 3. Take the *sum* of these products.

# Voting again with Karnaugh Maps

| Α | В | С | M |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

### **Building Blocks**

Microarchitecture

Abstraction!

Processor datapath

**Instruction Decoder** Arithmetic Logic Unit

Memory

**Digital Logic**

Adders Multiplexers **Demultiplexers Encoders Decoders**

Registers

Flip-Flops Latches

Gates

**Devices** (transistors, etc.)

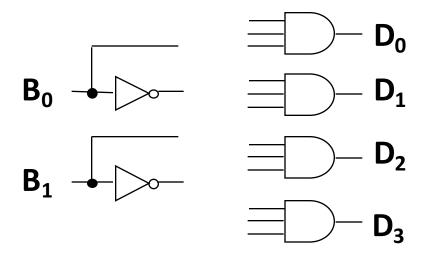

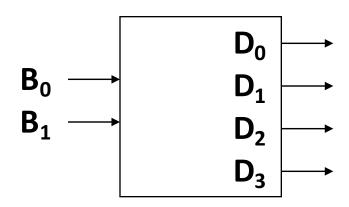

### **Decoders**

Decodes input number, asserts corresponding output.

*n*-bit input (an unsigned number)

$2^n$  outputs

Built with code detectors.

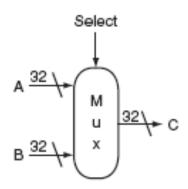

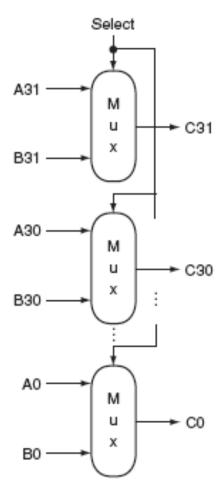

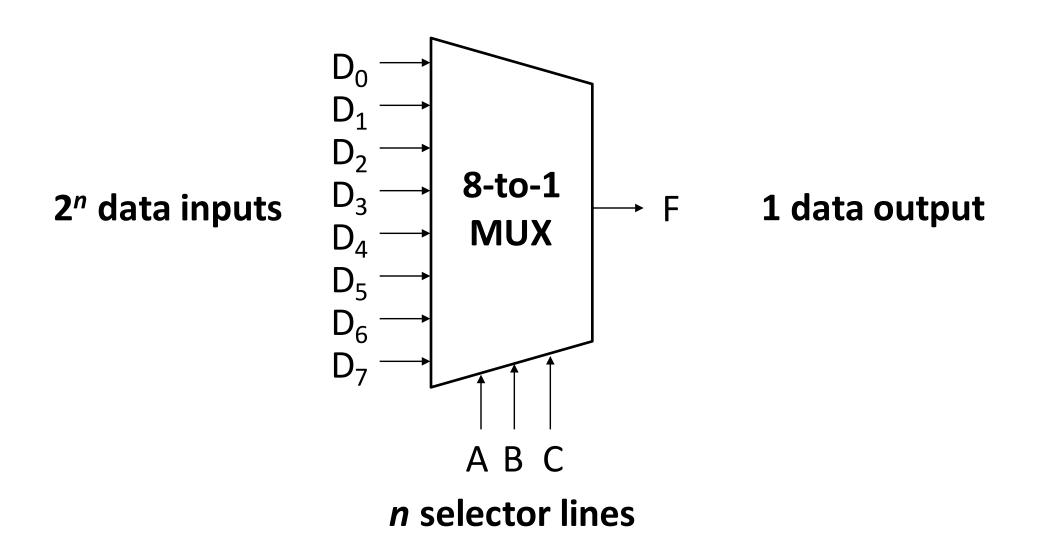

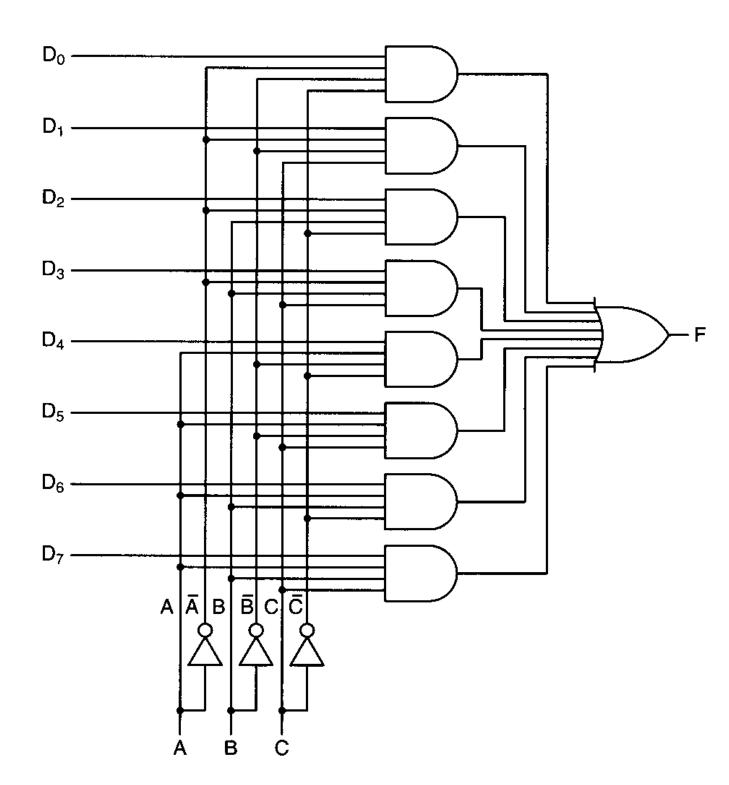

### Multiplexers

Select one of several inputs to forward as output.

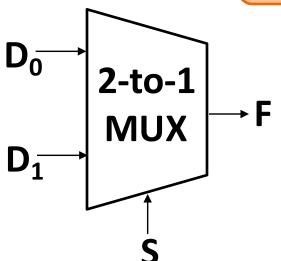

# Build a 2-to-1 MUX from gates

ex

If S=0, then  $F=D_0$ . If S=1, then  $F=D_1$ .

1. Construct the truth table.

2. Build the circuit.

### 8-to-1 MUX

Costume idea: MUX OX

### **MUX** + voltage source = truth table

### Buses and Logic Arrays

A **bus** is a collection of data lines treated as a single logical signal.

= fixed-width value

**Array of logic elements** applies same operation to each bit in a bus.

= bitwise operator