CS 240 Spring 2020 Foundations of Computer Systems Ben Wood

CS 240 Spring 2020 Foundations of Computer Systems Ben Wood

# Memory Hierarchy and Cache

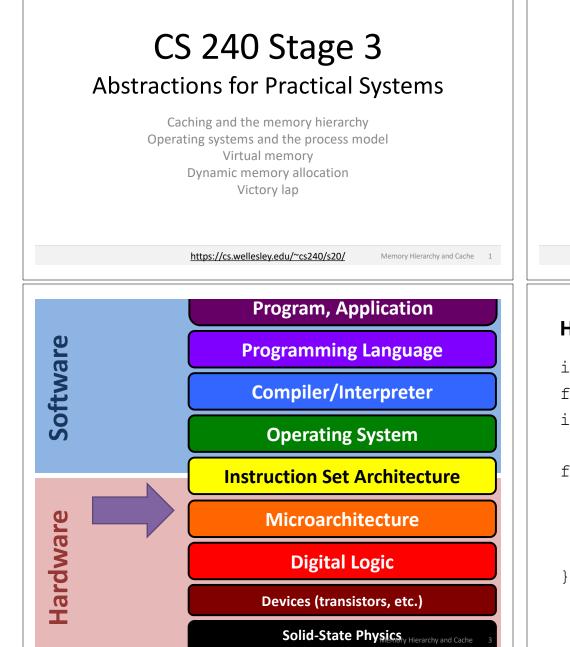

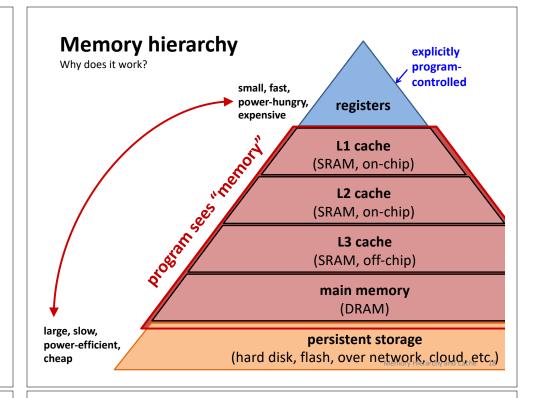

Memory hierarchy Cache basics Locality Cache organization Cache-aware programming

https://cs.wellesley.edu/~cs240/s20/

Memory Hierarchy and Cache 2

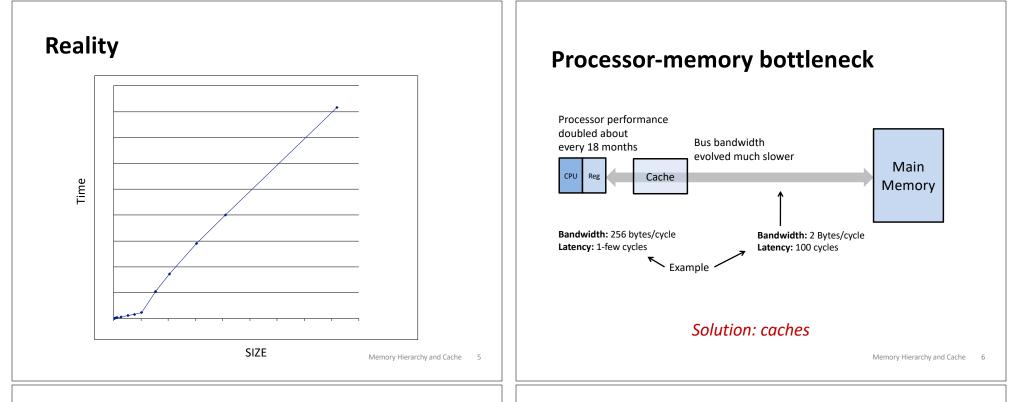

## How does execution time grow with SIZE?

Memory Hierarchy and Cache 7

## Cache

### English:

*n.* a hidden storage space for provisions, weapons, or treasures*v.* to store away in hiding for future use

### **Computer Science:**

**n.** a computer memory with short access time used to store frequently or recently used instructions or data

v. to store [data/instructions] temporarily for later quick retrieval

Also used more broadly in CS: software caches, file caches, etc.

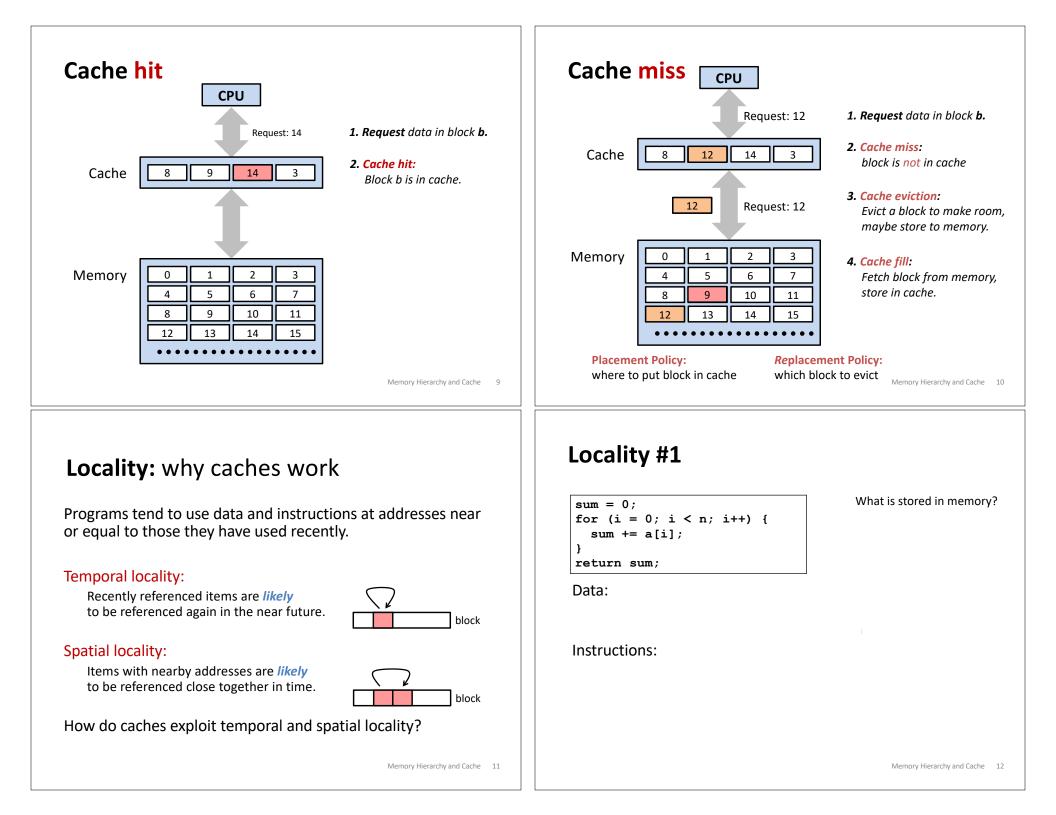

#### **General cache mechanics** CPU Block: unit of data in cache and memory. (a.k.a. line) Smaller, faster, more expensive. 9 Cache 8 14 3 🖌 Stores subset of memory blocks. (lines) Data is moved in block units Larger, slower, cheaper. Memory 3 0 1 2 Partitioned into blocks (lines). 4 5 6 7 8 9 10 11 12 13 14 15 Memory Hierarchy and Cache 8

## **Cache performance metrics**

### **Miss Rate**

Fraction of memory accesses to data not in cache (misses / accesses) Typically: 3% - 10% for L1; maybe < 1% for L2, depending on size, etc.

### **Hit Time**

Time to find and deliver a block in the cache to the processor. Typically: **1 - 2 clock cycles** for L1; **5 - 20 clock cycles** for L2

### **Miss Penalty**

Additional time required on cache miss = main memory access time Typically **50 - 200 cycles** for L2 (*trend: increasing!*)

Memory Hierarchy and Cache 17

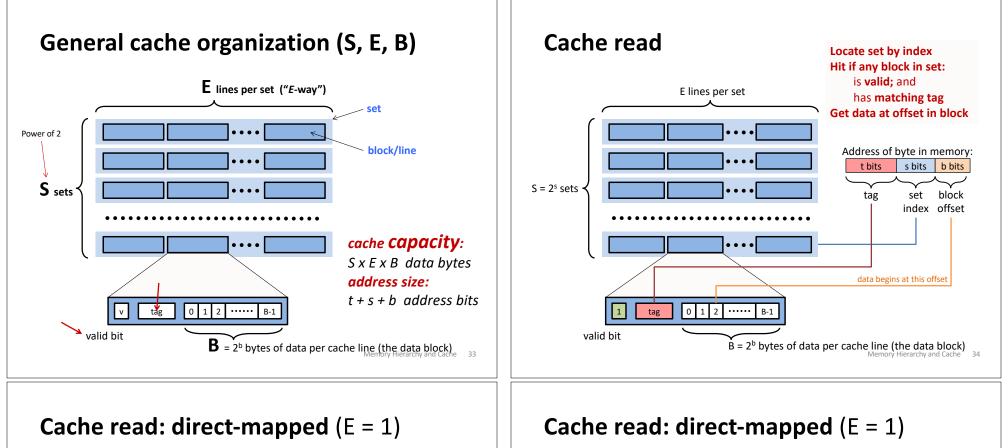

## **Cache organization**

### Block

Fixed-size unit of data in memory/cache

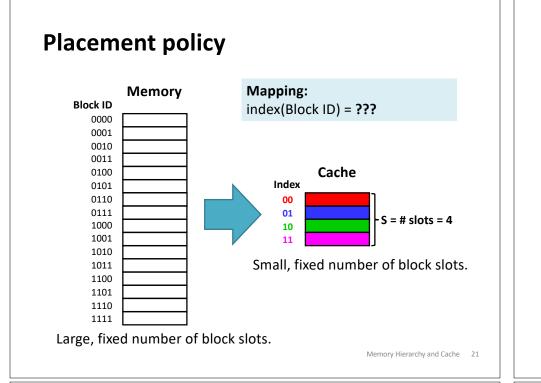

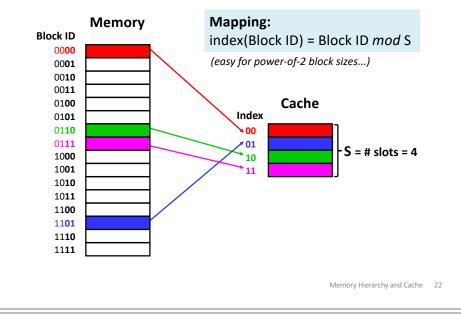

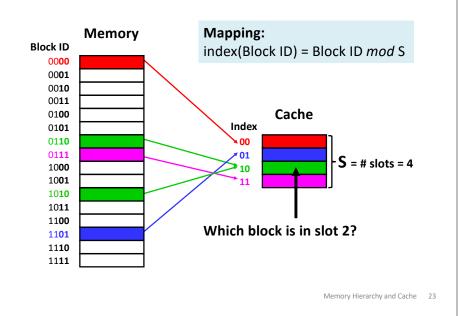

### **Placement Policy**

Where in the cache should a given block be stored?

direct-mapped, set associative

### **Replacement Policy**

What if there is no room in the cache for requested data?

least recently used, most recently used

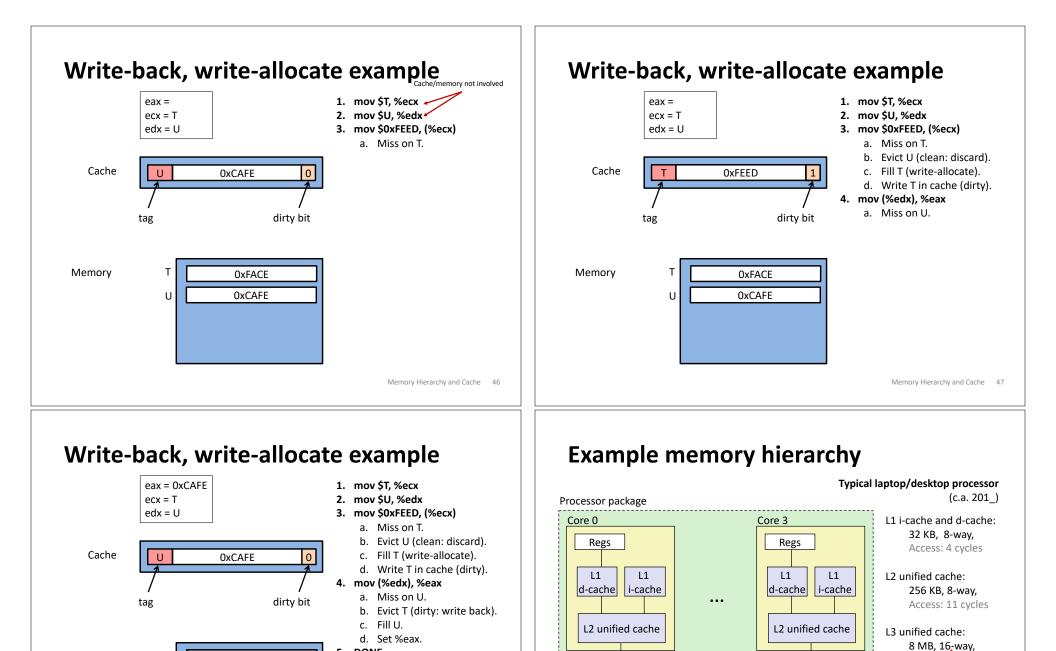

### Write Policy

When should writes update lower levels of memory hierarchy?

write back, write through, write allocate, no write allocate

Memory Hierarchy and Cache 19

#### (byte) address Memory **Blocks** 00000000 Note: drawing address order differently from here on Divide address space into fixed-size aligned blocks. block power of 2 0 Example: block size = 8 **00001**000 full byte address block 1 00010010 < 00010000 00010001 00010010 Block ID offset within block 00010013 block 00010100 address bits - offset bits log<sub>2</sub>(block size) 00010101 2 00010110 00010111 00011000 block 3 Memory Hiererchy and Cache 20 remember withinSameBlock? (Pointers Lab)

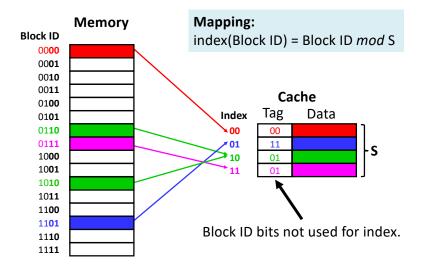

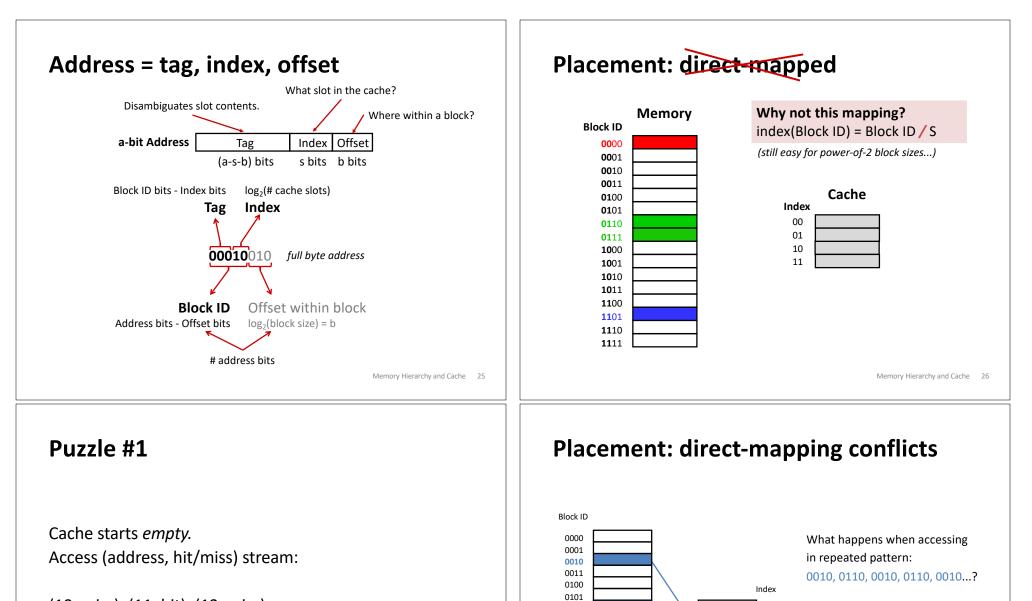

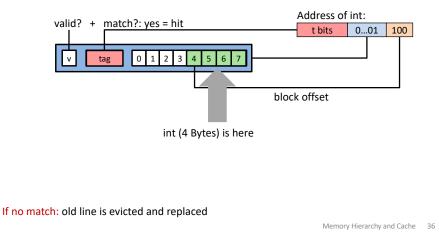

## Placement: direct-mapped

## Placement: mapping ambiguity?

## Placement: tags resolve ambiguity

(10, miss), (11, hit), (12, miss)

### What could the block size be?

Memory Hierarchy and Cache 27

Memory Hierarchy and Cache 28

cache conflict

by next access.

Every access suffers a miss,

evicts cache line needed

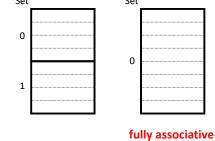

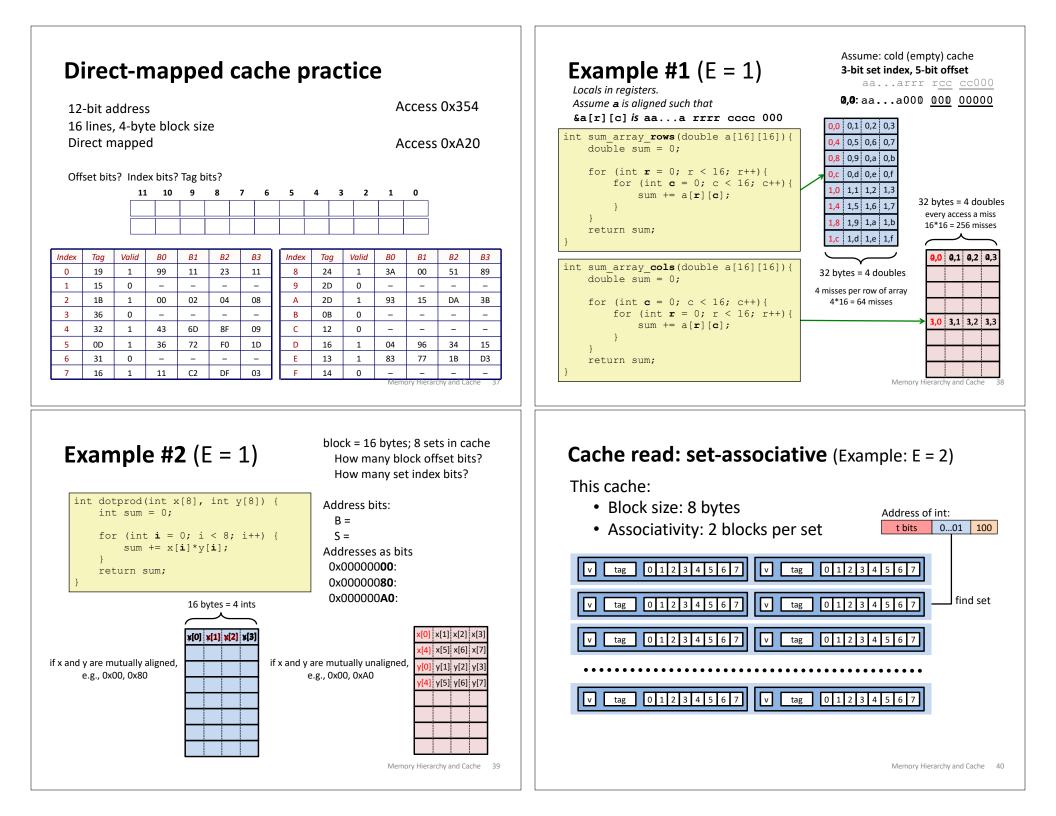

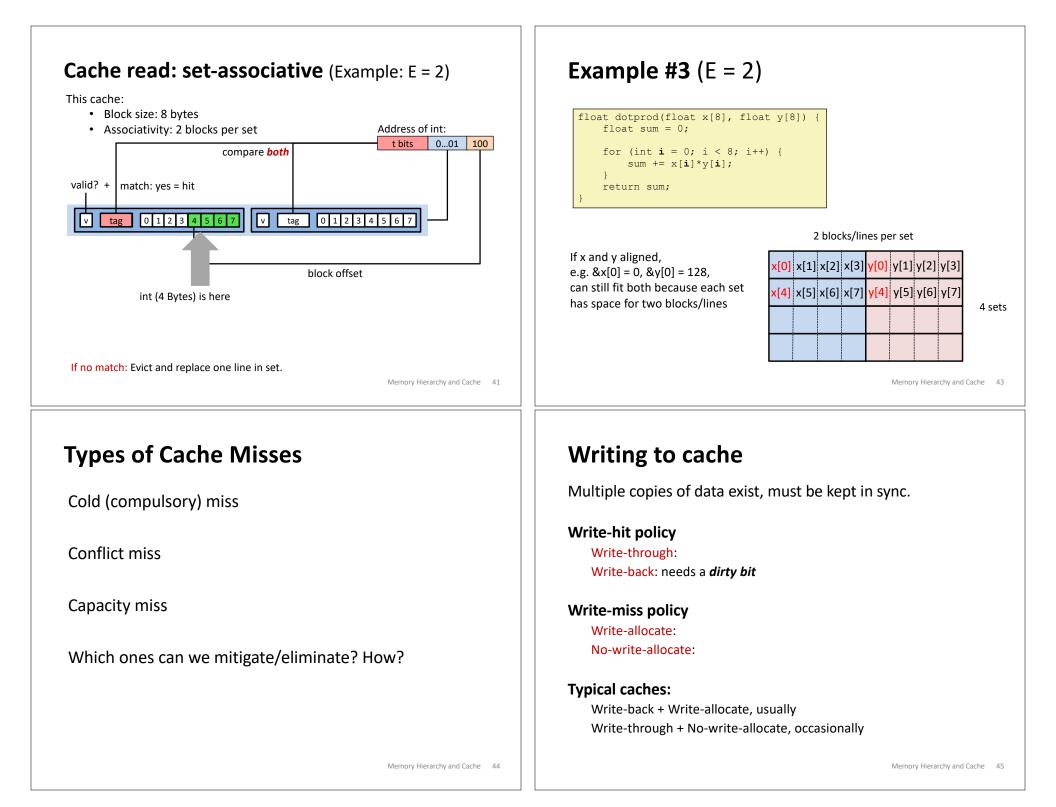

### Placement: set-associative

One index per set of block slots. Store block in *any* slot within set.

2

3

1-way 8 sets.

1 block each

direct mapped

Set

0

1

2

3

4

5

6

7

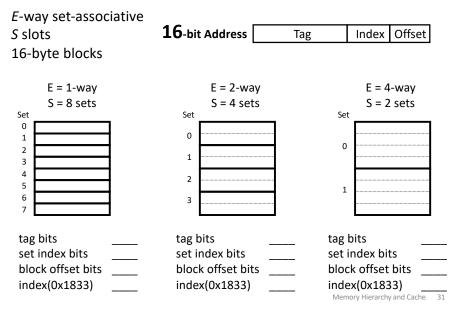

#### Mapping: index(Block ID) = Block ID mod S 2-wav 4-wav 8-wav 4 sets. 2 sets. 1 set, 2 blocks each 4 blocks each 8 blocks Set Set Set 0 0 1

sets

S = # stars in cache

**Replacement policy:** if set is full, what block should be replaced? Common: least recently used (LRU) but hardware may implement "not most recently used"

## Example: tag, index, offset? #2

## Example: tag, index, offset? #1 **4**-bit Address Tag Index Offset **Direct-mapped** tag bits 4 slots set index bits 2-byte blocks block offset bits index(1101) = Memory Hierarchy and Cache 30

## **Replacement policy**

If set is full, what block should be replaced? Common: least recently used (LRU) (but hardware usually implements "not most recently used"

Another puzzle: Cache starts *empty*, uses LRU. Access (address, hit/miss) stream: (10, miss); (12, miss); (10, miss)

associativity of cache?

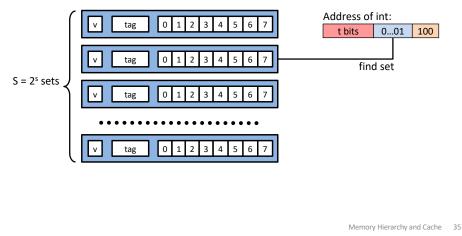

This cache:

- Block size: 8 bytes

- Associativity: 1 block per set (direct mapped)

This cache:

- Block size: 8 bytes

- Associativity: 1 block per set (direct mapped)

Memory Hierarchy and Cache 48

5. DONE.

Memory

Т

U

**0xFEED**

**0xCAFE**

Main memory

L3 unified cache

(shared by all cores)

Access: 30-40 cycles

slower, but

more likely

Block size: 64 bytes for

Memory Hierarchy and Cache 49

all caches.

## (Aside) Software caches

### Examples

File system buffer caches, web browser caches, database caches, network CDN caches, etc.

### Some design differences

Almost always fully-associative

Often use complex replacement policies

Not necessarily constrained to single "block" transfers

Memory Hierarchy and Cache 50

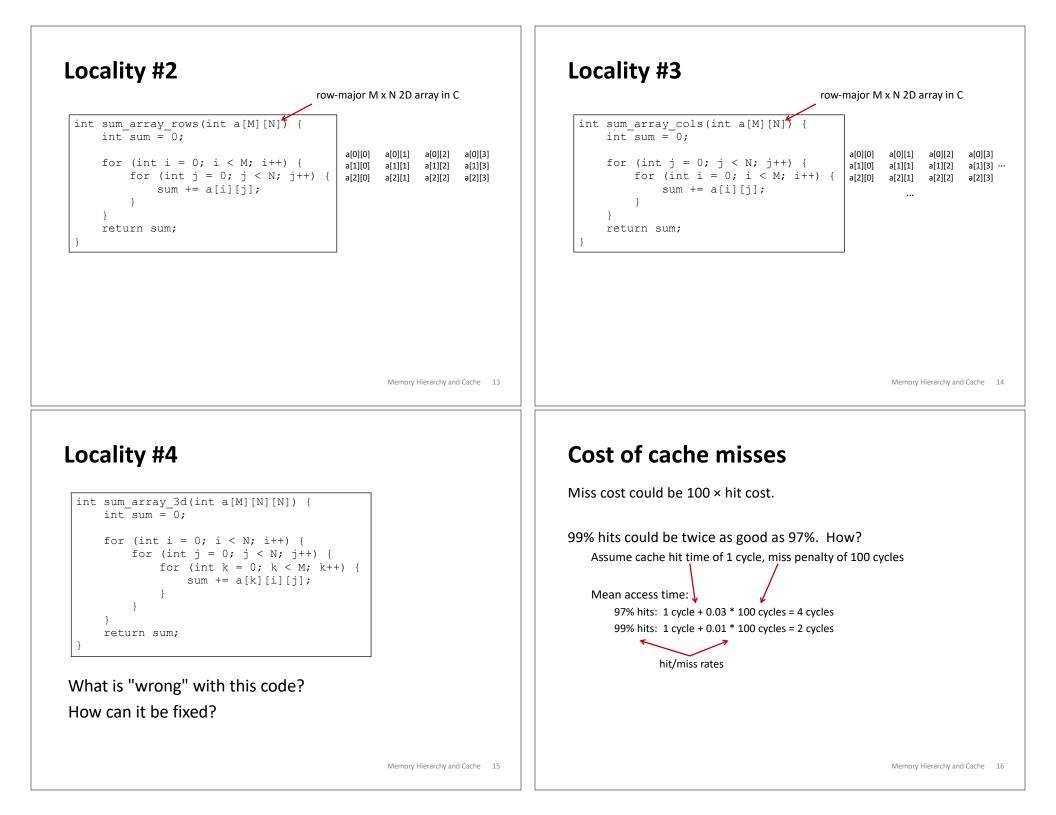

## **Cache-friendly code**

Locality, locality, locality. Programmer can optimize for cache performance Data structure layout Data access patterns Nested loops Blocking (see CSAPP 6.5) All systems favor "cache-friendly code" Performance is hardware-specific Generic rules capture most advantages Keep working set small (temporal locality) Use small strides (spatial locality) Focus on inner loop code

Memory Hierarchy and Cache 51