# Virtual Memory

Process Abstraction, Part 2: Private Address Space

**Motivation**: why not direct physical memory access?

Address translation with pages

Optimizing translation: translation lookaside buffer

Extra benefits: sharing and protection

Memory as a contiguous array of bytes is a lie! Why?

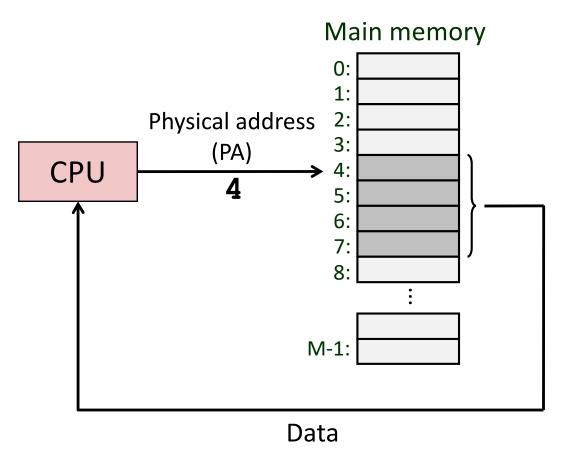

# Problems with physical addressing

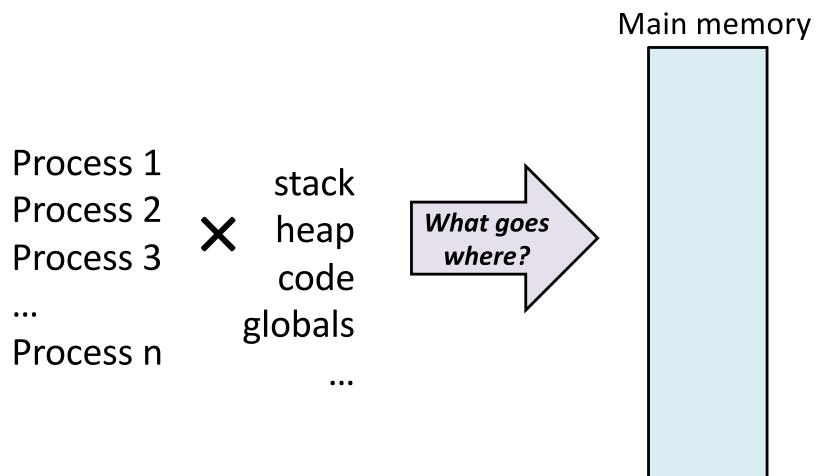

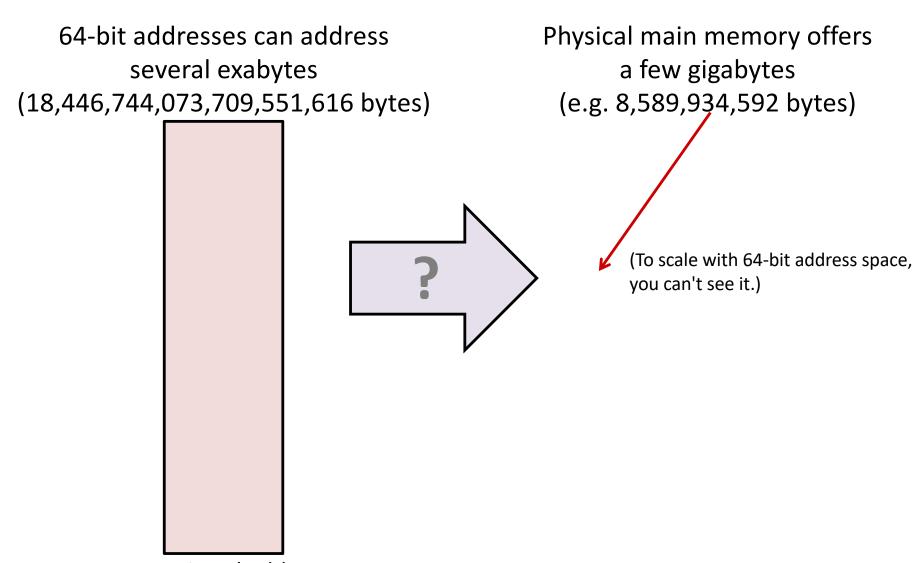

# **Problem 1: memory management**

#### Also:

**Context switches** must swap out entire memory contents. Isn't that **expensive**?

# **Problem 2: capacity**

1 virtual address space per process, with many processes...

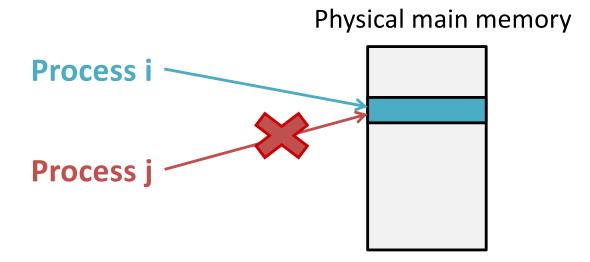

## **Problem 3: protection**

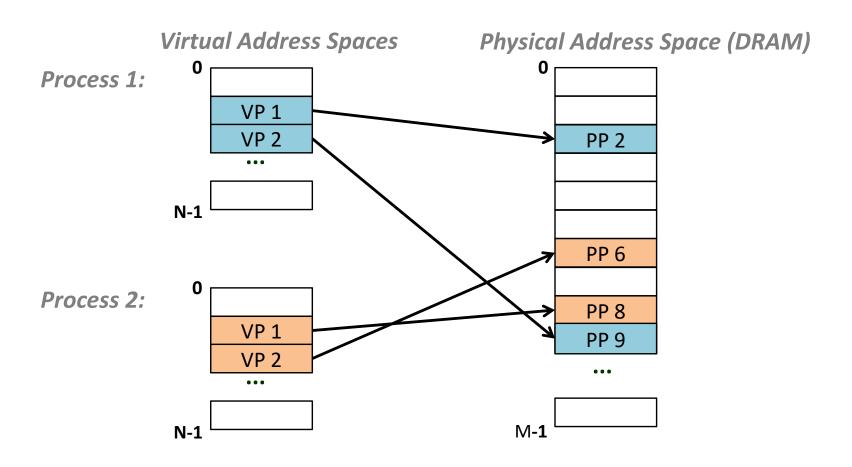

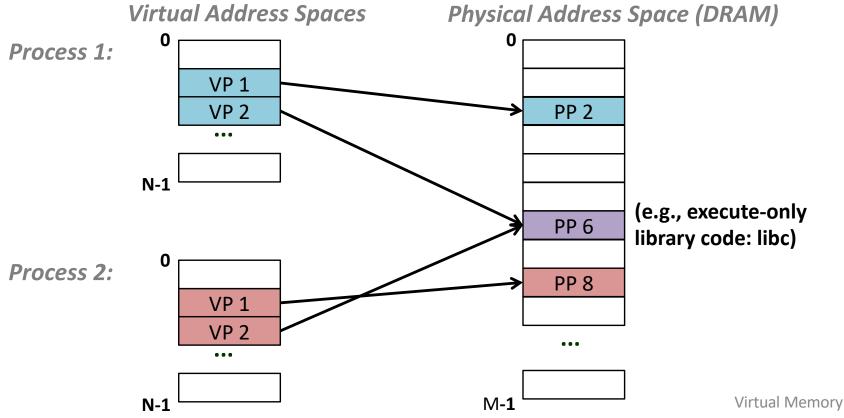

### **Problem 4: sharing**

Process i

Process j

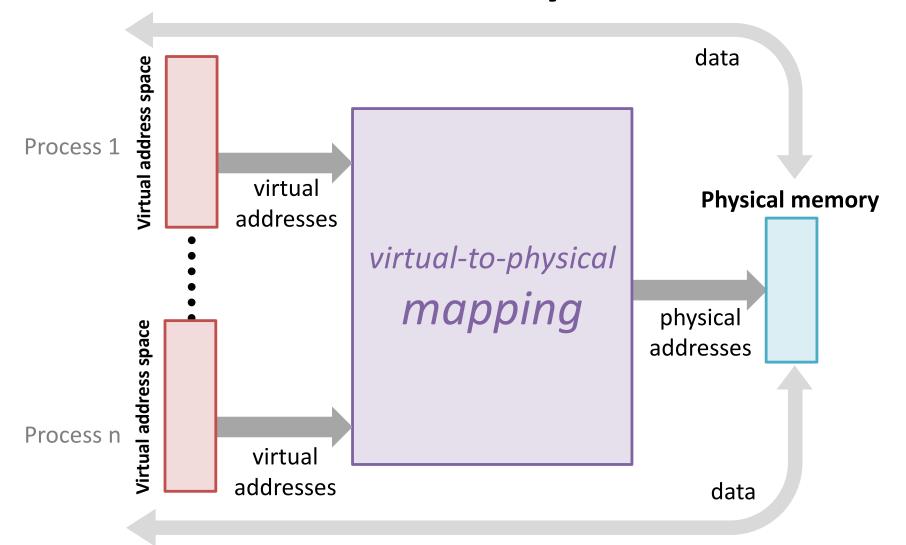

### Solution: Virtual Memory (address indirection)

Private virtual address space per process.

Single physical address space managed by OS/hardware.

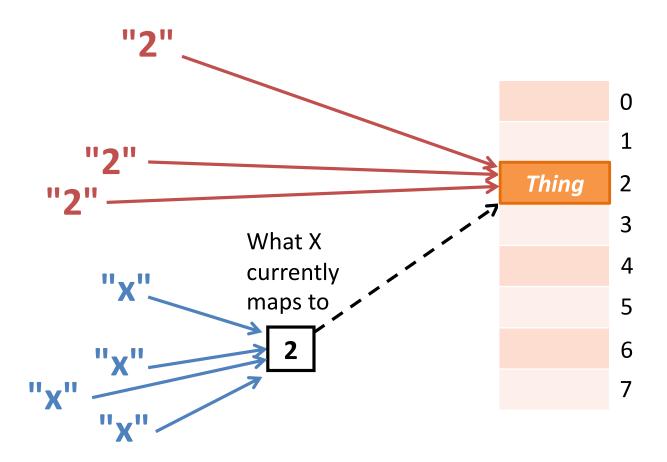

#### Indirection

(it's everywhere!)

Direct naming

Indirect naming

What if we move *Thing*?

## Tangent: indirection everywhere

- Pointers

- Constants

- Procedural abstraction

- Domain Name Service (DNS)

- Dynamic Host Configuration Protocol (DHCP)

- Phone numbers

- 911

- Call centers

- Snail mail forwarding

"Any problem in computer science can be solved by adding another level of indirection."

-David Wheeler, inventor of the subroutine, or Butler Lampson

## Virtual addressing and address translation

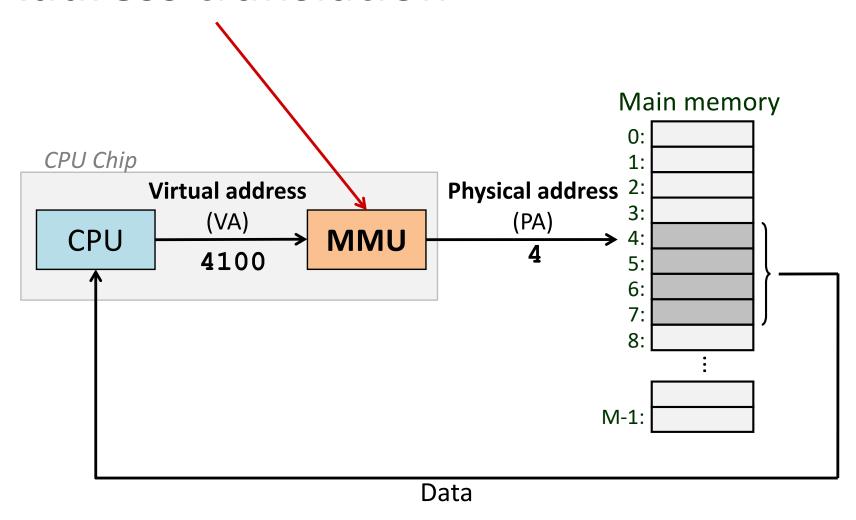

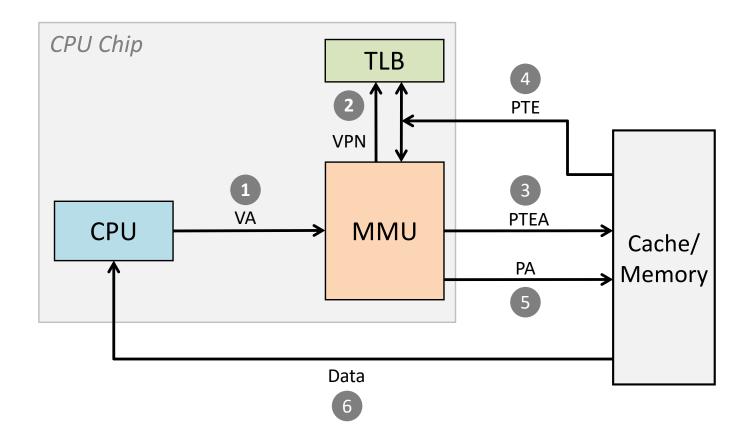

#### **Memory Management Unit**

translates virtual address to physical address Main memory 0: CPU Chip 1: Physical address 2: Virtual address (VA) (PA) **MMU CPU** 4: 4 4100 5: 6: 8: M-1: Data

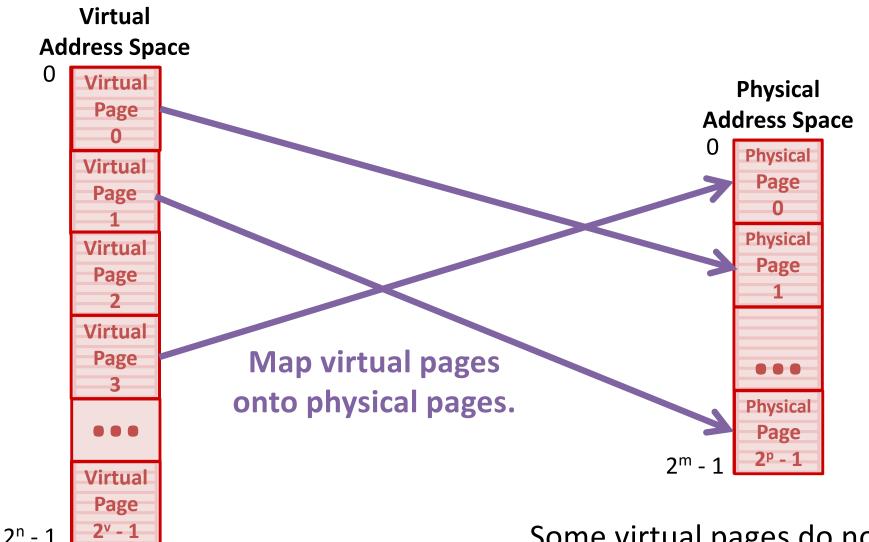

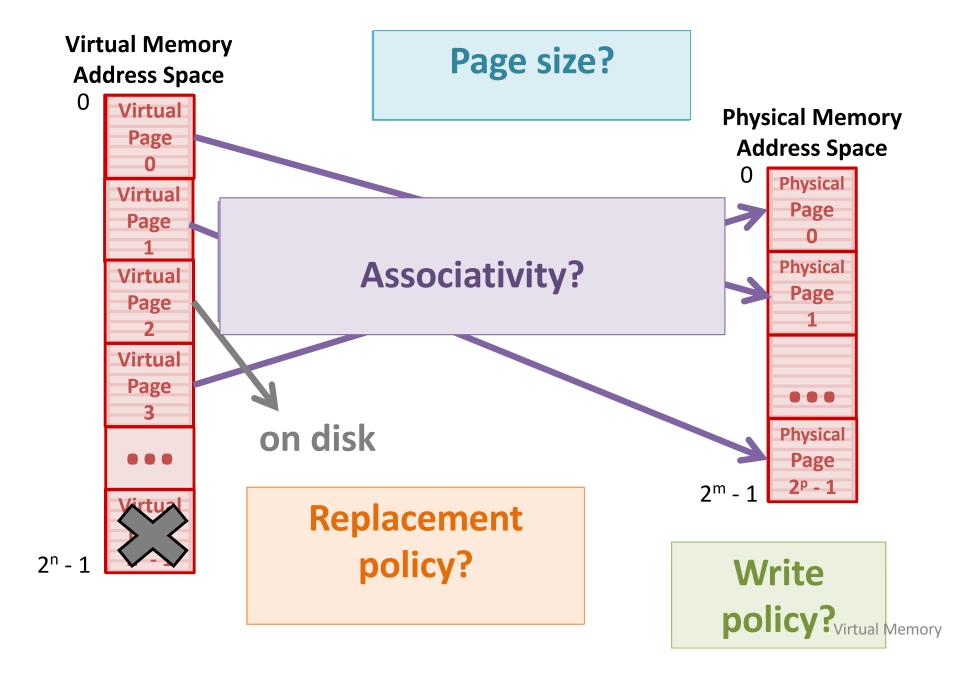

## Page-based mapping

fixed-size, aligned *pages*page size = power of two

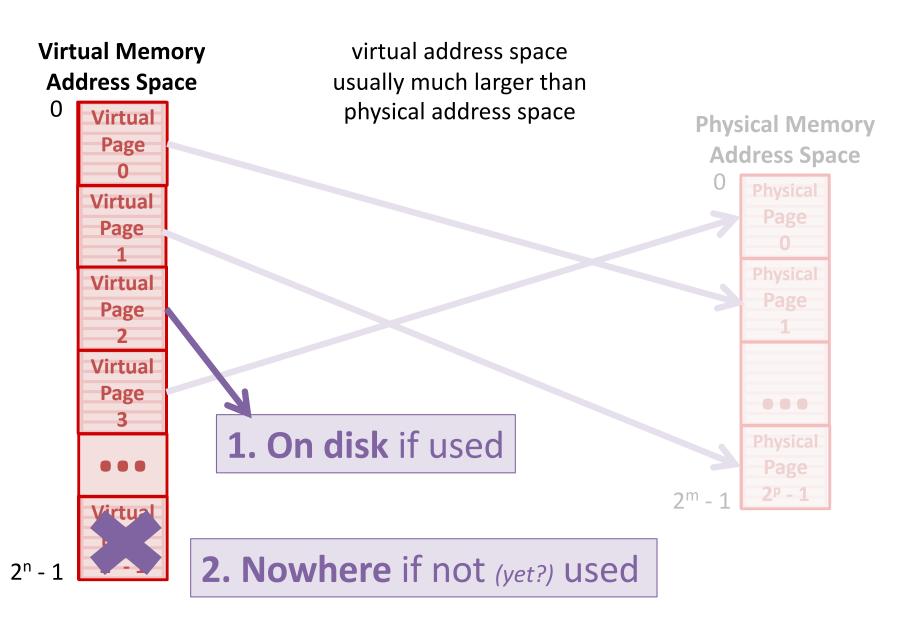

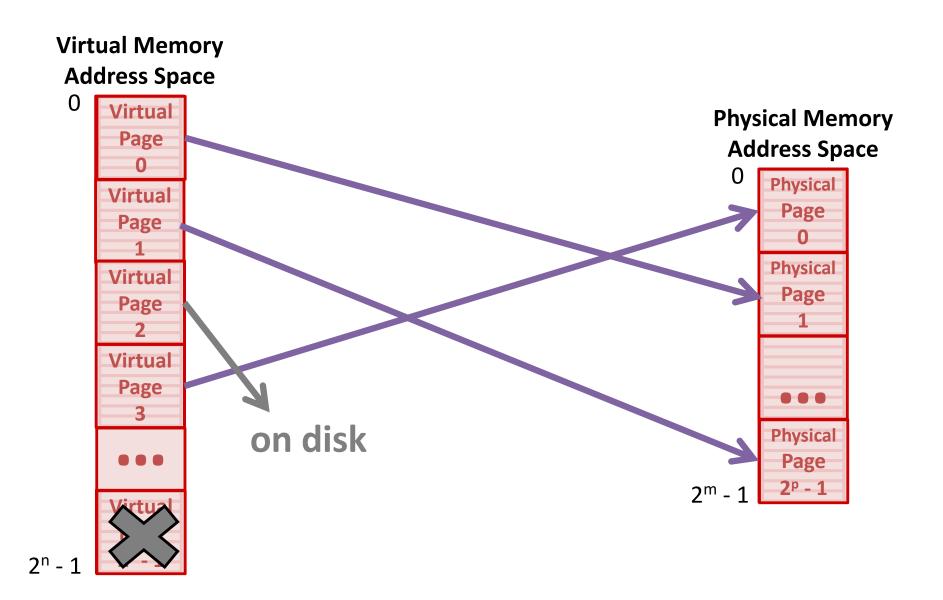

Some virtual pages do not fit! Where are they stored?

#### Cannot fit all virtual pages! Where are the rest stored?

# Virtual memory: cache for disk?

# Design for a slow disk: exploit locality

# Design for a slow disk: exploit locality

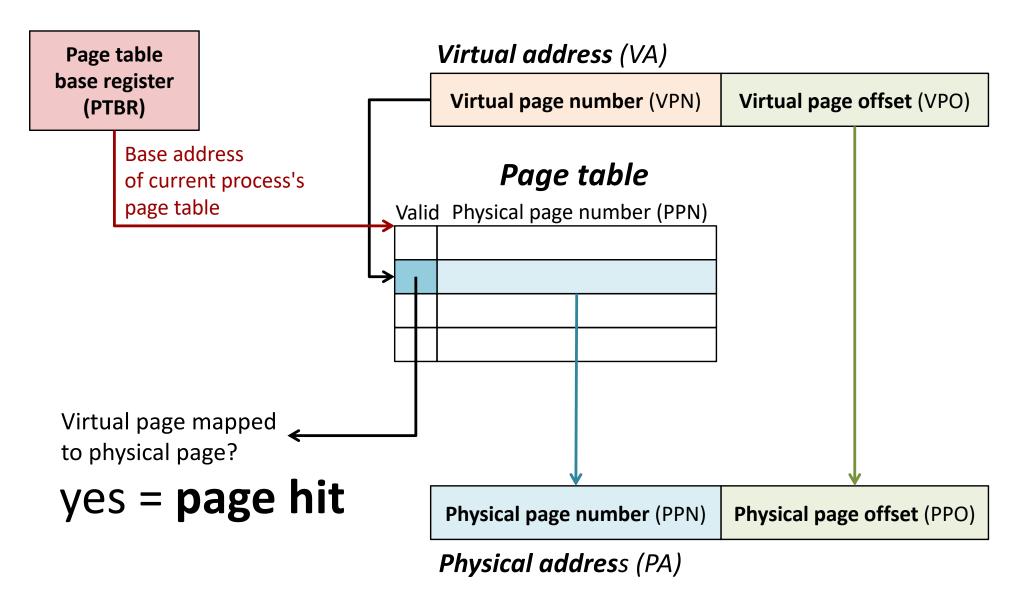

#### Address translation

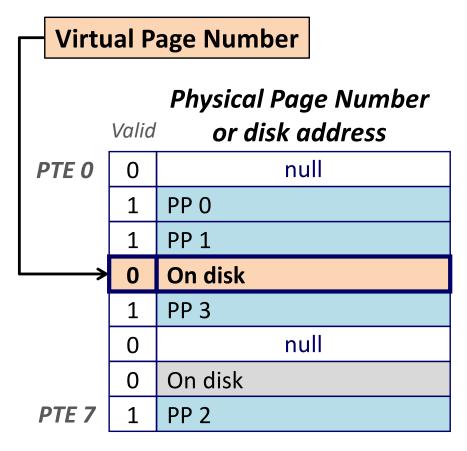

# Page table

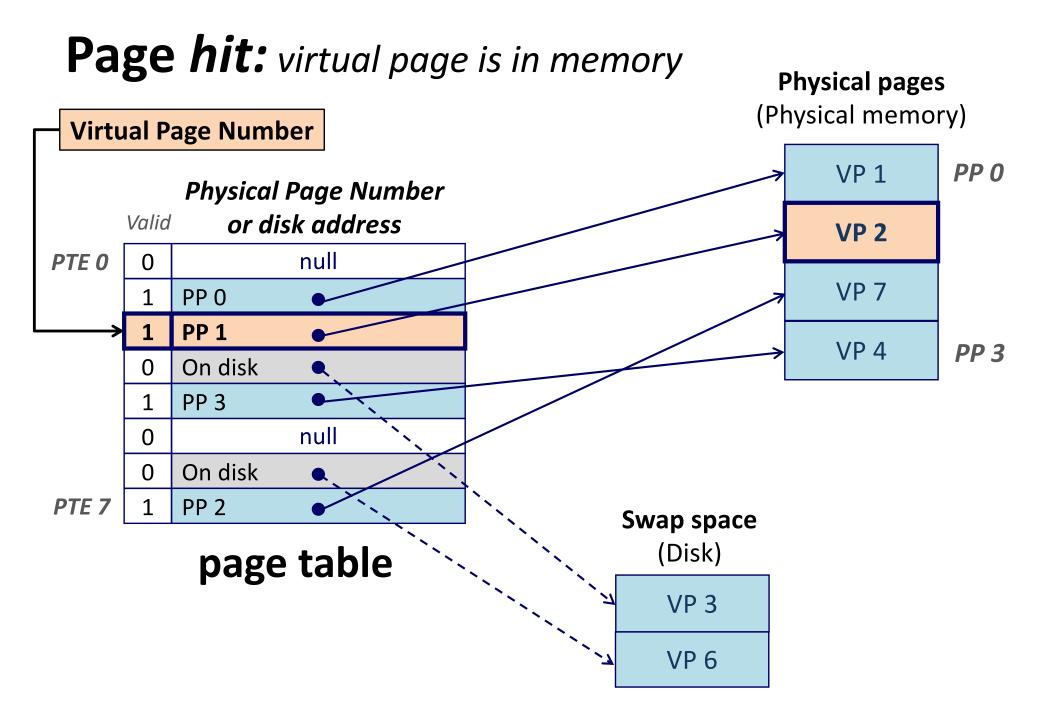

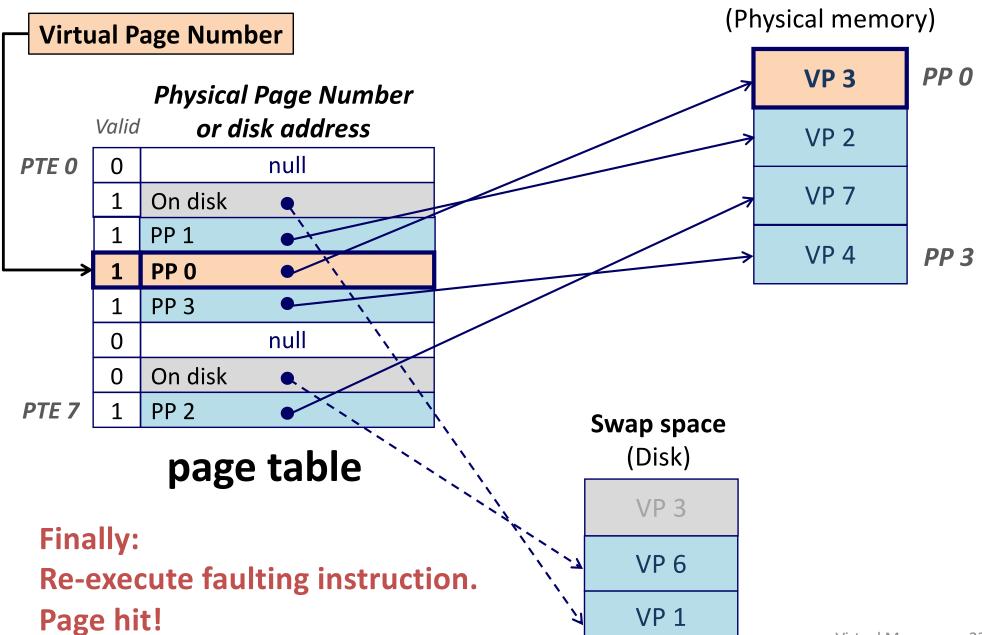

**Physical pages** array of *page table entries* (PTEs) (Physical memory) mapping virtual page to where it is stored PP 0 VP<sub>1</sub> Physical Page Number Valid or disk address VP 2 PTE 0 null 0 VP 7 1 1 VP 4 PP 3 0 1 null 0 0 PTE 7 **Swap space** (Disk) page table VP3 Memory resident, VP 6 managed by HW (MMU), OS

# Address translation with a page table

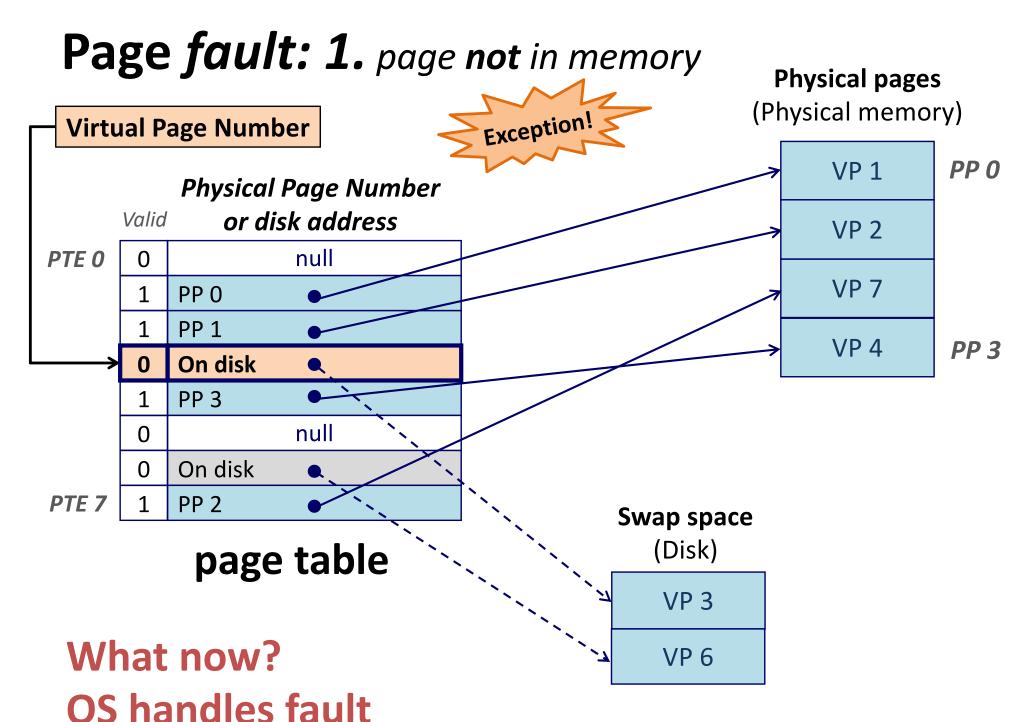

# Page fault:

page table

#### Physical pages

(Physical memory)

| VP 1             | VP 1 |

|------------------|------|

| VP 2 <i>PP 1</i> | VP 2 |

| VP 7 <i>PP 2</i> | VP 7 |

| VP 4 <b>PP</b> 3 | VP 4 |

**Swap space**

(Disk)

VP 3

VP 6

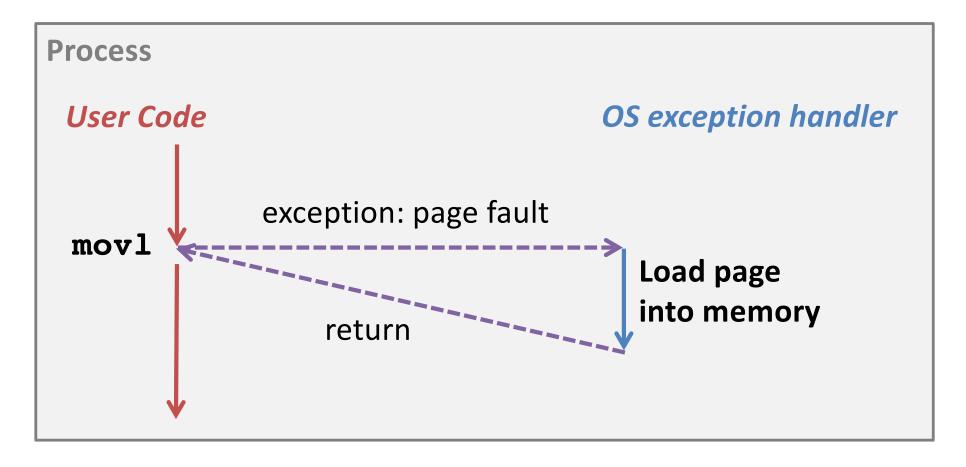

## Page fault: exceptional control flow

Process accessed virtual address in a page that is not in physical memory.

Returns to faulting instruction: **mov1** is executed *again*!

**Physical pages**

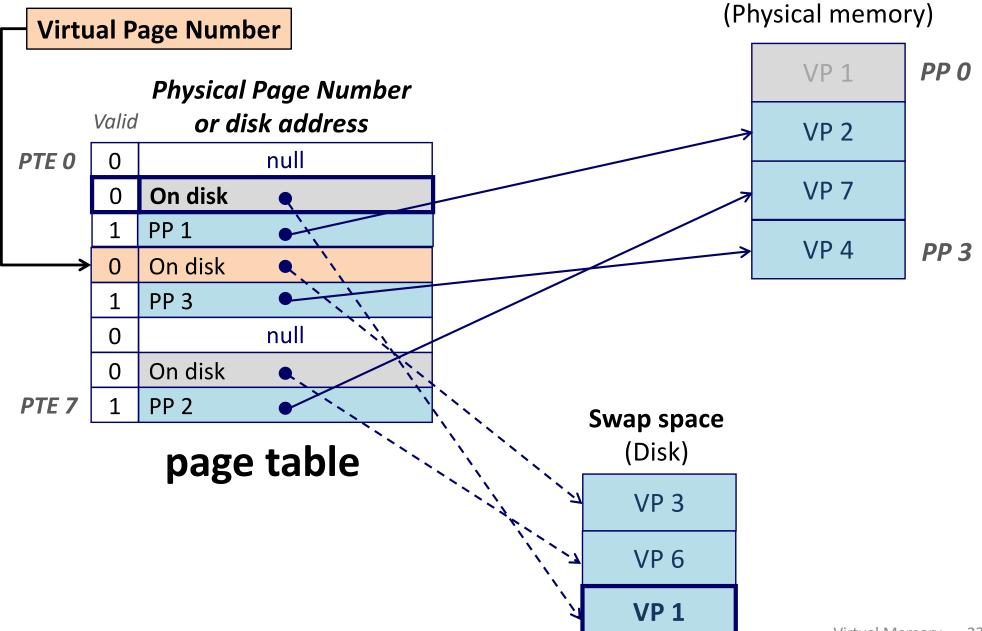

Page fault: 2. OS evicts another page.

**Physical pages**

Page fault: 3. OS loads needed page.

# **Terminology**

#### context switch

Switch control between processes on the same CPU.

#### page in

Move page of virtual memory from disk to physical memory.

#### page out

Move page of virtual memory from physical memory to disk.

#### thrash

Total working set size of processes is larger than physical memory. Most time is spent paging in and out instead of doing useful work.

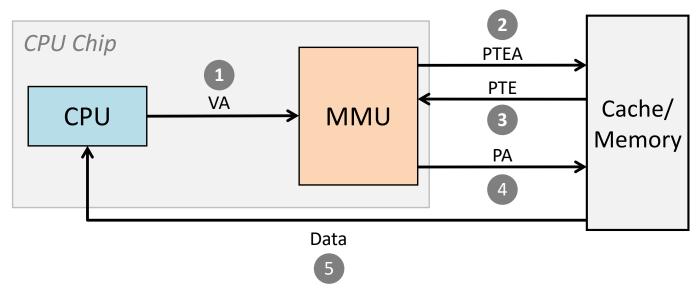

## Address translation: page hit

- 1) Processor sends virtual address to MMU (memory management unit)

- 2-3) MMU fetches PTE from page table in cache/memory

- 4) MMU sends physical address to cache/memory

- 5) Cache/memory sends data word to processor

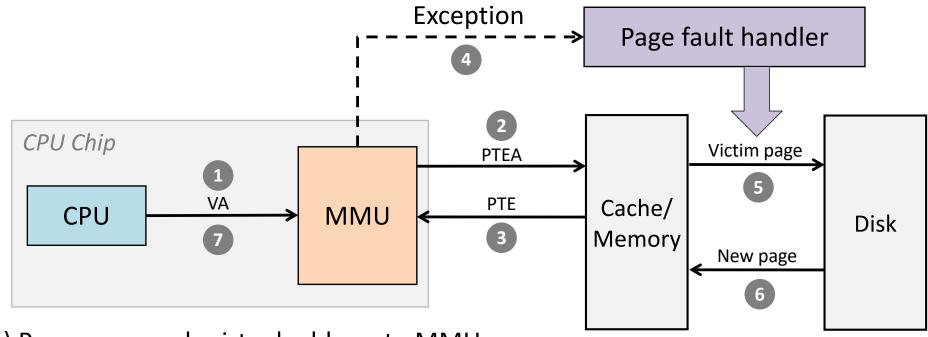

# Address Translation: Page Fault

- 1) Processor sends virtual address to MMU

- 2-3) MMU fetches PTE from page table in cache/memory

- 4) Valid bit is zero, so MMU triggers page fault exception

- 5) Handler identifies victim (and, if dirty, pages it out to disk)

- 6) Handler pages in new page and updates PTE in memory

- 7) Handler returns to original process, restarting faulting instruction

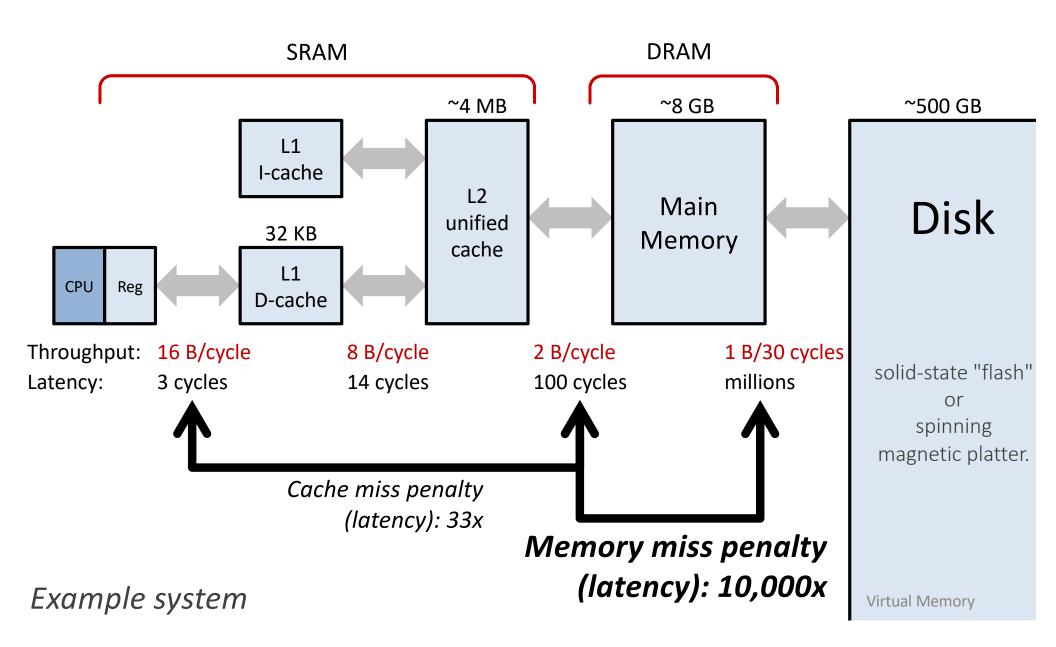

#### How fast is translation?

How many physical memory accesses are required to complete one virtual memory access?

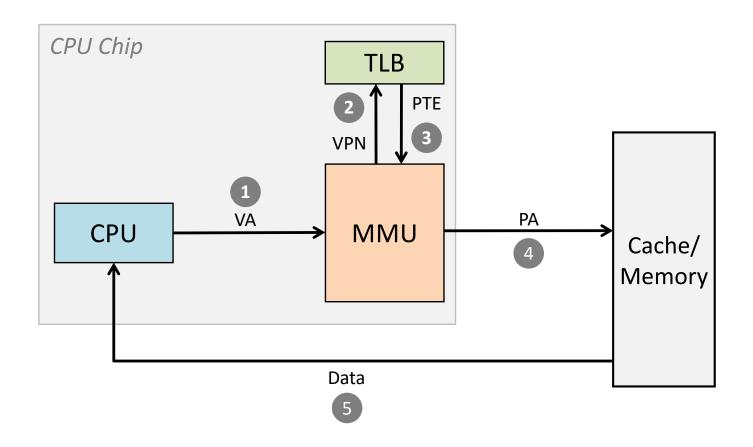

# **Translation Lookaside Buffer (TLB)**

Small hardware cache in MMU just for page table entries e.g., 128 or 256 entries

Much faster than a page table lookup in memory.

In the running for "un/classiest name of a thing in CS"

#### **TLB** hit

#### A TLB hit eliminates a memory access

#### **TLB** miss

#### A TLB miss incurs an additional memory access (the PTE)

Fortunately, TLB misses are rare. Does a TLB miss require disk access?

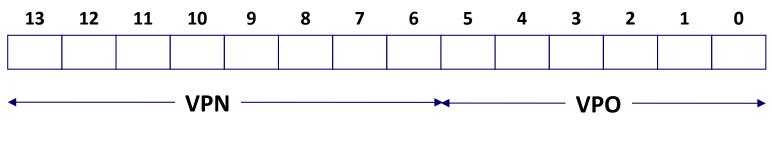

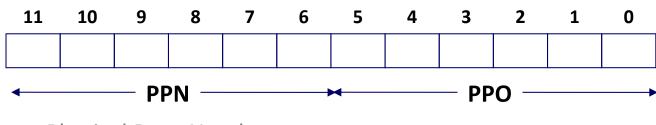

# Memory system example (small)

#### Addressing

14-bit virtual addresses

12-bit physical address

Page size = 64 bytes

Simulate accessing these virtual addresses on the system: 0x03D4, 0x0B8F, 0x0020

Virtual Page Number

Virtual Page Offset

Physical Page Number

Physical Page Offset

# Memory system example: page table

Only showing first 16 entries (out of  $256 = 2^8$ )

virtual page #\_\_\_ TLB index\_\_\_ TLB tag \_\_\_ TLB Hit? \_\_ Page Fault? \_\_ physical page #: \_\_\_

| VPN | PPN | Valid |

|-----|-----|-------|

| 00  | 28  | 1     |

| 01  | 1   | 0     |

| 02  | 33  | 1     |

| 03  | 02  | 1     |

| 04  | 1   | 0     |

| 05  | 16  | 1     |

| 06  | _   | 0     |

| 07  | _   | 0     |

| VPN | PPN | Valid |

|-----|-----|-------|

| 08  | 13  | 1     |

| 09  | 17  | 1     |

| 0A  | 09  | 1     |

| ОВ  | _   | 0     |

| 0C  | 1   | 0     |

| 0D  | 2D  | 1     |

| 0E  | 11  | 1     |

| OF  | 0D  | 1     |

What about a real address space? Read more in the book...

# Memory system example: TLB

#### 16 entries

4-way associative

virtual page #\_\_\_\_ TLB index\_\_\_\_ TLB tag \_\_\_\_ TLB Hit? \_\_ Page Fault? \_\_ physical page #: \_\_\_\_

| Set | Tag | PPN | Valid |

|-----|-----|-----|-------|-----|-----|-------|-----|-----|-------|-----|-----|-------|

| 0   | 03  | _   | 0     | 09  | 0D  | 1     | 00  | _   | 0     | 07  | 02  | 1     |

| 1   | 03  | 2D  | 1     | 02  | _   | 0     | 04  | _   | 0     | 0A  | _   | 0     |

| 2   | 02  | _   | 0     | 08  | _   | 0     | 06  | _   | 0     | 03  | _   | 0     |

| 3   | 07  | _   | 0     | 03  | 0D  | 1     | 0A  | 34  | 1     | 02  | _   | 0     |

TLB ignores page offset. Why?

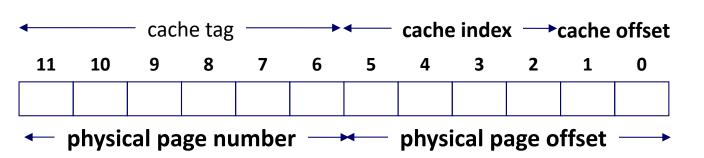

## Memory system example: cache

16 lines4-byte block sizePhysically addressedDirect mapped

| cache offset | cache index | cache tag | Hit? | Byte: |

|--------------|-------------|-----------|------|-------|

|--------------|-------------|-----------|------|-------|

| Idx | Tag | Valid | В0 | B1 | B2 | В3 |

|-----|-----|-------|----|----|----|----|

| 0   | 19  | 1     | 99 | 11 | 23 | 11 |

| 1   | 15  | 0     | 1  | 1  | 1  | 1  |

| 2   | 1B  | 1     | 00 | 02 | 04 | 08 |

| 3   | 36  | 0     | -  | -  | _  | _  |

| 4   | 32  | 1     | 43 | 6D | 8F | 09 |

| 5   | 0D  | 1     | 36 | 72 | F0 | 1D |

| 6   | 31  | 0     | _  | _  | _  | _  |

| 7   | 16  | 1     | 11 | C2 | DF | 03 |

| Idx | Tag | Valid | <i>B0</i> | B1 | B2 | B3 |

|-----|-----|-------|-----------|----|----|----|

| 8   | 24  | 1     | 3A        | 00 | 51 | 89 |

| 9   | 2D  | 0     | _         | _  | _  | _  |

| Α   | 2D  | 1     | 93        | 15 | DA | 3B |

| В   | OB  | 0     | _         | _  | _  | _  |

| С   | 12  | 0     | _         | _  | _  | _  |

| D   | 16  | 1     | 04        | 96 | 34 | 15 |

| Е   | 13  | 1     | 83        | 77 | 1B | D3 |

| F   | 14  | 0     | _         | _  | _  | _  |

# Virtual memory benefits: Simple address space allocation

Process needs private *contiguous* address space.

Storage of virtual pages in physical pages is fully associative.

## Virtual memory benefits:

## Simple cached access to storage > memory

Good locality, or least "small" working set = mostly page hits

All necessary page table entries fit in TLB

Working set pages fit in physical memory

If combined working set > physical memory:

Thrashing: Performance meltdown. CPU always waiting or paging.

#### Full indirection quote:

"Every problem in computer science can be solved by adding another level of indirection, but that usually will create another problem."

## Virtual memory benefits:

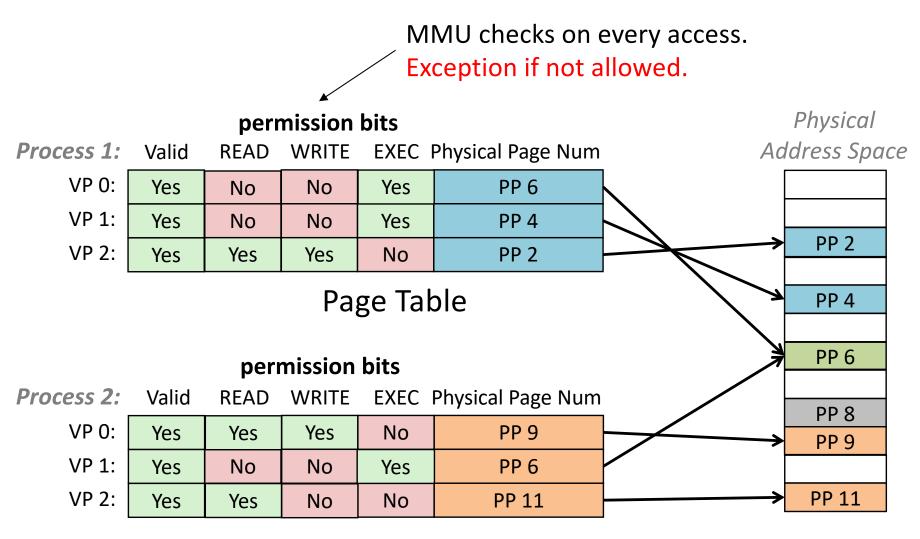

#### **Protection:**

All accesses go through translation.

Impossible to access physical memory not mapped in virtual address space.

## **Sharing:**

Map virtual pages in separate address spaces to same physical page (PP 6).

# Virtual memory benefits: **Memory permissions**

Page Table

## Summary: virtual memory

#### Programmer's view of virtual memory

Each process has its own private linear address space Cannot be corrupted by other processes

#### System view of virtual memory

Uses memory efficiently (due to locality) by caching virtual memory pages

Simplifies memory management and sharing Simplifies protection -- easy to interpose and check permissions

#### More goodies:

- Memory-mapped files

- Cheap fork() with copy-on-write pages (COW)

## Summary: memory hierarchy

#### L1/L2/L3 Cache: Pure Hardware

Purely an optimization

"Invisible" to program and OS, no direct control

Programmer cannot control caching, can write code that fits well

#### Virtual Memory: Software-Hardware Co-design

Supports processes, memory management

Operating System (software) manages the mapping

Allocates physical memory

Maintains page tables, permissions, metadata

Handles exceptions

Memory Management Unit (hardware) does translation and checks

Translates virtual addresses via page tables, enforces permissions

TLB caches the mapping

Programmer cannot control mapping, can control sharing/protection via OS