# Laboratory 5 Instruction Set Architecture and Microarchitecture

In computer science, an **Instruction Set Architecture** (**ISA**) is an abstract model of a computer.

At a minimum, the ISA specifies:

- **size of address bus:** specifies the size of the memory in the computer (and, therefore, the number of address bits required),

- **size of data bus:** specifies the size of an instruction and the size of a standard data value stored in a register (and, therefore, the **number of data bits** required),

- the **number of registers** in the CPU: used to store values when executing instructions, and

- the **formats and meaning of the instructions** which can be executed in the CPU.

A microarchitecture is a concrete implementation of an ISA.

We will define an ISA for a machine we call the **HW** machine, and we will then use LogicWorks to implement a working microarchitecture that we can experiment with and test.

#### **HW Instruction Set Architecture**

- 8 bit address bus so, instruction memory has  $2^8 = 256$  bytes

- 16 bit data bus so, each instruction is 16 bits (2 bytes), and each register will hold 16 bits of data

- 16 registers R0 = 0 (constant) R1 =1 (constant) R2-R15 general purpose

| HW ISA             | Instructions                                                  | MSB 16-bit Encoding LSB |     |     |        |

|--------------------|---------------------------------------------------------------|-------------------------|-----|-----|--------|

| Assembly Syntax    | Meaning                                                       | Opcode                  | Rs  | Rt  | Rd     |

| ADD Rs, Rt, Rd     | $R[d] \leftarrow R[s] + R[t]$                                 | 0010                    | S   | t   | d      |

| SUB Rs, Rt, Rd     | $R[d] \leftarrow R[s] - R[t]$                                 | 0011                    | S   | t   | d      |

| AND Rs, Rt, Rd     | $R[d] \leftarrow R[s] \& R[t]$                                | 0100                    | s   | t   | d      |

| OR Rs, Rt, Rd      | $R[d] \leftarrow R[s] \mid R[t]$                              | 0101                    | s   | t   | d      |

| BEQ Rs, Rt, offset | If $R[s] == R[t]$ then<br>PC $\leftarrow$ PC + 2 + (offset*2) | 0111                    | s   | t   | offset |

| JMP offset         | PC ← offset*2                                                 | 1000                    | o f | f s | e t    |

For a complete definition of a computer, it is also necessary to define instructions which can transfer values between the CPU and memory.

We omit those here because we only have time to consider a subset of the necessary instructions in a single lab.

#### **Fetch Instruction from Memory**

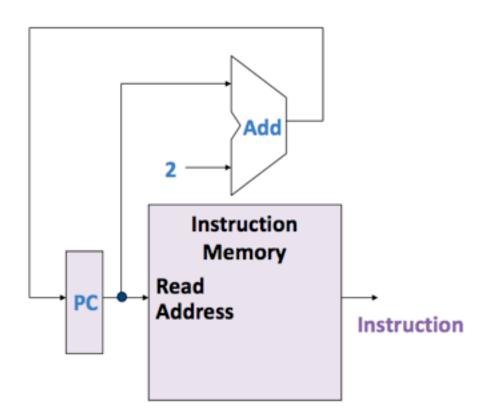

Remember the fetch instruction circuit at the end of our last lab?

Programs are stored as instructions in memory. The first instruction in the program is assumed to start at address 0 in memory.

The **Program Counter (PC)** register holds the address of the currently executing instruction.

The **PC** is initialized to 0 by a **reset** to begin execution of the program.

The instruction in memory at the address from PC is fetched (read at the outputs of the memory). It is then sent to the CPU to be executed.

The PC is incremented by 2.

Steps 1 and 2 are repeated until all instructions are executed.

This model assumes that all instructions in a program are always executed in sequential order.

However, the instruction in programs do not always execute in sequential order!

You must sometimes skip some instructions (like when you have to go to the **else** clause of an **if** statement, you skip the **if** clause). For example:

if (x < 0)

y = 2; // skip this statement when the condition is not met

else

y = 3;</pre>

Or, you may need to go back to an earlier instruction (like when you get to the end of **loop**, you have to get back to the beginning of the loop to repeat it).

### **BEQ (Branch-if -EQual)**

In our **HW** machine, the **BEQ** (**Branch-if-EQual**) instruction allows us to *conditionally* change the sequential order of execution of instructions:

# BEQ Rs Rt offset

This instruction compares the contents of **Rs** and **Rt** and calculates a new address to branch to if the registers' contents are equal.

The branch address is calculated relative to the address of the next sequential instruction in memory:

# **PC + 2**

The **offset** is the number of instructions away that the branch address is from the usual next sequential instruction.

The **offset** is a *signed* value (it can be either positive or negative), and is specified as a 4-bit value. So, it can range from -8 to +7 in our **HW** machine.

Since each instruction is two bytes, the offset is multiplied by 2 and added to the address of the next sequential instruction to calculate the branch address. This formula can be expressed as:

**PC + 2 + (2\*offset)**

For example, suppose you have executed the first few instructions of a program and the next ones are:

| 6:  | <b>BEQ R3 R0 1</b> |

|-----|--------------------|

| 8:  | ADD R1 R2 R2       |

| 10: | AND R0 R0 R4       |

When executing **BEQ R3 R0 1**, **PC** contains address 6 and offset = 1.

If, at that point, **R3** contains a 0, then **R3** and **R0** contain equal values, and so the next value of the **PC** will be 6 + 2 + (2\*1) = 10. Program execution will skip the instruction at address 8 and go straight to 10.

However, if **R3** does not contain a 0, the program will simply progress to the next address in memory, **PC + 2**, which will be 6 + 2 = 8.

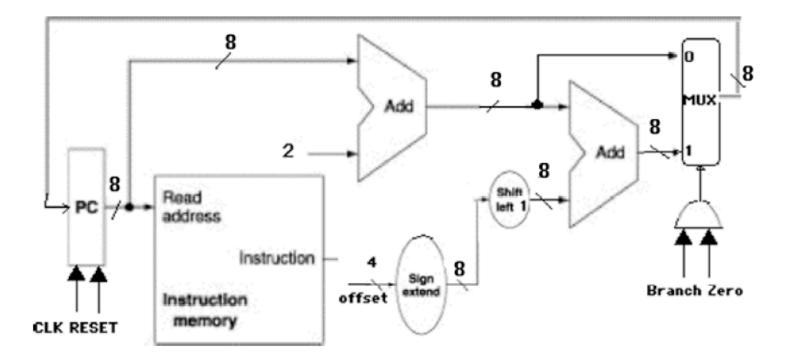

We add the following logic to our existing instruction fetch circuit to implement **BEQ**:

A MUX (multiplexer) selects the next value of the PC, either PC+2 (calculated by the first adder), or PC + 2 + 2\*offset (calculated by the second adder).

The MUX selects which address to use based on two control bits, Zero and Branch.

On a **BEQ** instruction, the ALU subtracts the contents of **Rs** from **Rt**. The **Zero** bit is set if the result is 0.

The **Branch** bit simply indicates that a **BEQ** instruction is being executed (other instruction may also set the **Zero** bit in the **ALU**, so it is necessary that both **Branch** = 1 and **Zero** = 1 for the branch address to be selected.

We will construct this circuit in LogicWorks to verify correct operation.

#### JMP (Jump)

In the HW computer, there is also an unconditional branch instruction called **JMP** (Jump):

#### JMP offset

Here, the **offset** is a 12-bit value which specifies the number of instructions from the beginning of the program to jump to:

### PC = offset \* 2

For example, **JMP 3** sets the **PC** to 6, causing the instruction stored at address 6 (*i.e.*, the 3rd instruction in the program) to be executed next.

### **CPU Datapath**

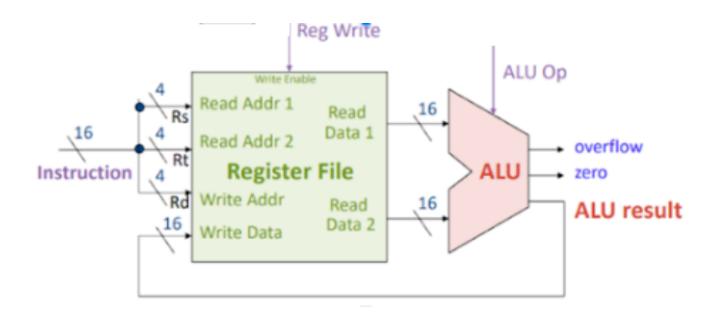

The following diagram describes the basic datapath for executing the arithmetic and logic instructions inside the CPU. It consists of a Register File and an ALU (you have studied both devices in previous labs).

This circuit can execute the arithmetic and logical operations including **ADD**,**SUB**,**AND**, and **OR**. The general form is:

op Rs Rt Rd

- read contents of Rs and Rt from Register File at Read Data 1 and Read Data 2 outputs

- perform an operation in the ALU on the contents of the registers (the ALUOp bits control which operation)

- write the ALU result back to register Rd in register file

The **ALUOp** bits are control signals that specify **AINV**, **BNEG**, and a 2bit operation (00 = AND, 01=OR, 10=+). Remember those from our study of the ALU?

The **RegWrite** control signal indicates whether a particular instruction results in a change to a register (some instructions do not change any registers).

The **ALUop** and **RegWrite** control lines are functions of the **opcode**, so there is some simple logic which can be used to produce these signals.

The following table shows the opcode for each instruction, and the associated control signals **ALUop** and **RegWrite** to be used for each.

| Instruction | Opcode | ALUop<br>Ainv Bneg Op1 Op0 | RegWrite |

|-------------|--------|----------------------------|----------|

| ADD         | 0010   | 0 0 1 0                    | 1        |

| SUB         | 0011   | 0 1 1 0                    | 1        |

| AND         | 0100   | 0 0 0 0                    | 1        |

| OR          | 0101   | 0 0 0 1                    | 1        |

| BEQ         | 0111   | 0 1 1 0                    | 0        |

| JMP         | 1000   | don't care                 | 0        |

**BEQ** is accomplished by subtraction (which sets the **Zero** bit).

**BEQ** and **JMP** do not change the value of a register.

**JMP** does not even use the **ALU** (it is implemented as part of the instruction fetch circuit)

In lab, you will connect the Register File to the ALU, and test its operation.

We won't get a chance to design how to produce the control signals, but you have seen how to do that in an earlier lab.

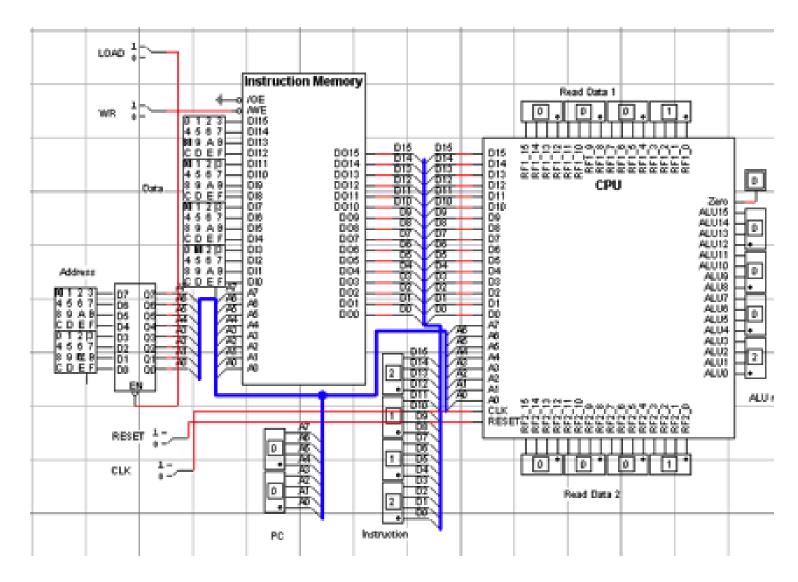

# **Full Implementation**

Finally, we abstract the **datapath** circuit into a **CPU** device, and connect it to our circuit for loading and fetching instructions from memory to execute a program.

You are given this circuit:

You will translate a short program from assembly language to machine code, load the instructions into memory, and then execute the instructions to run the program.