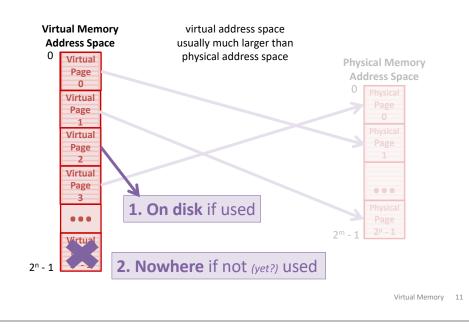

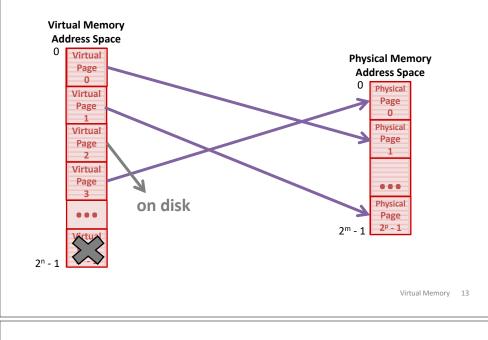

### Cannot fit all virtual pages! Where are the rest stored?

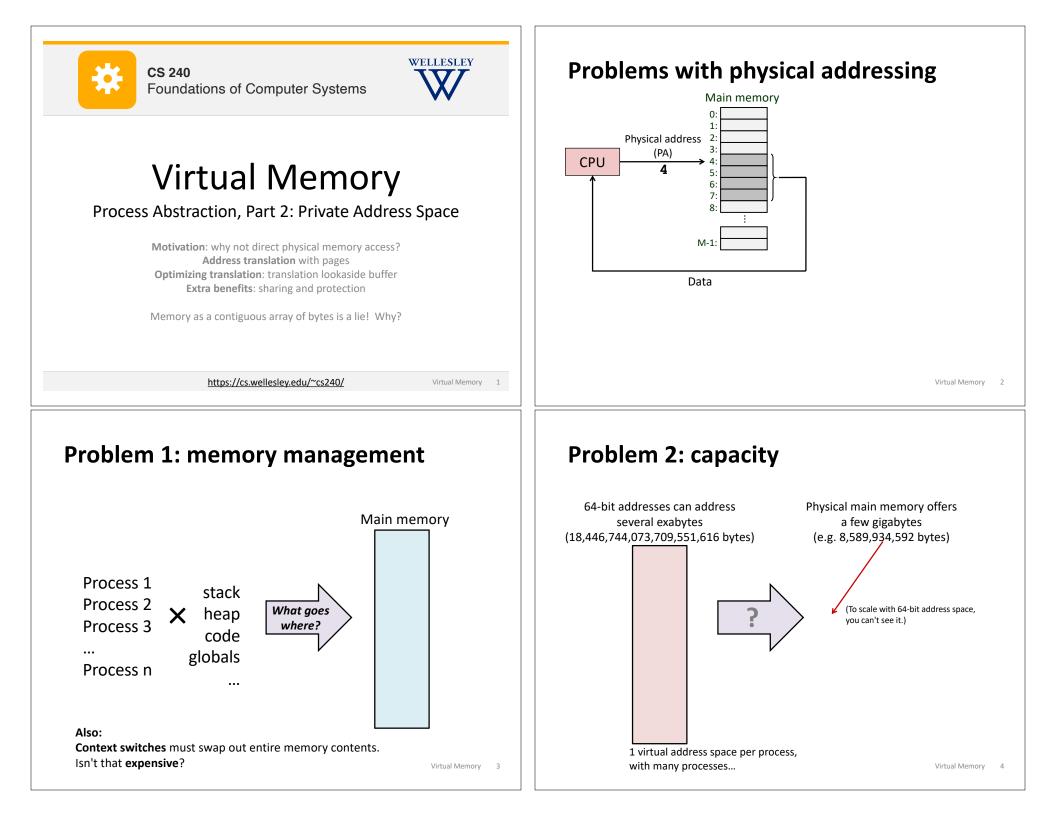

Data

Physical addresses are invisible to programs. 9

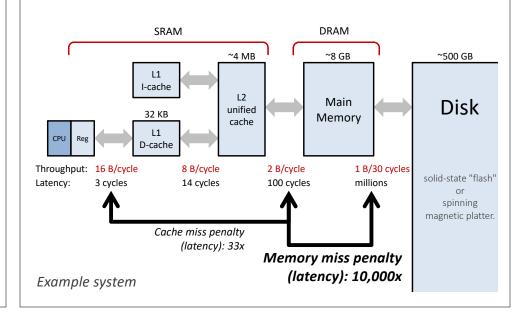

# Virtual memory: cache for disk?

...

Virtual

Page 2<sup>v</sup> - 1

2<sup>n</sup> - 1

Page 2<sup>p</sup> - 1

Virtual Memory 10

Not drawn to scale

2<sup>m</sup> - 1

Where are they stored?

Some virtual pages do not fit!

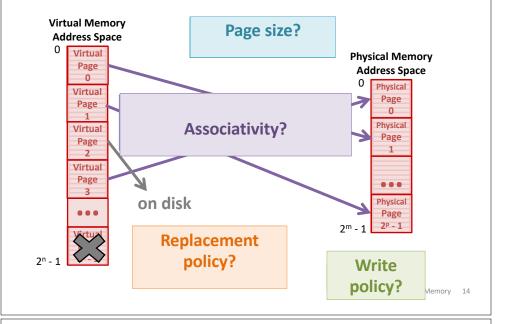

## Design for a slow disk: exploit locality

## Design for a slow disk: exploit locality

#### Address translation Main memory 0: CPU Chip 1 Virtual address Physical address 2: 3 (VA) (PA) MMU CPU 4 л 4100 5 6 7: 8 M-1: Data Virtual Memory 15

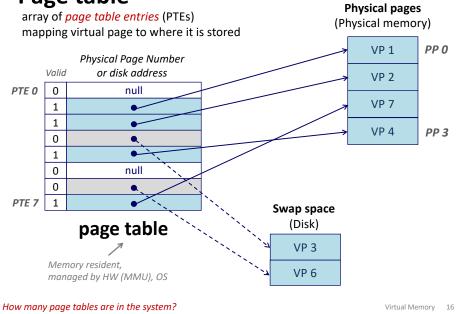

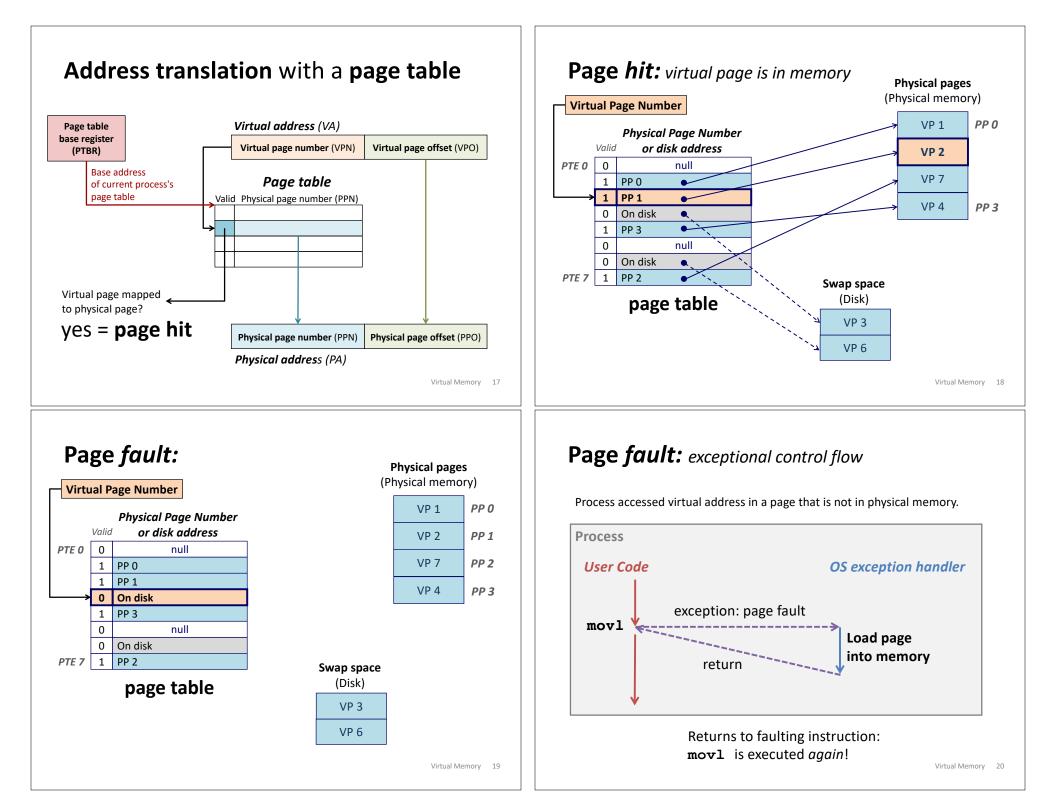

# Page table

# Terminology

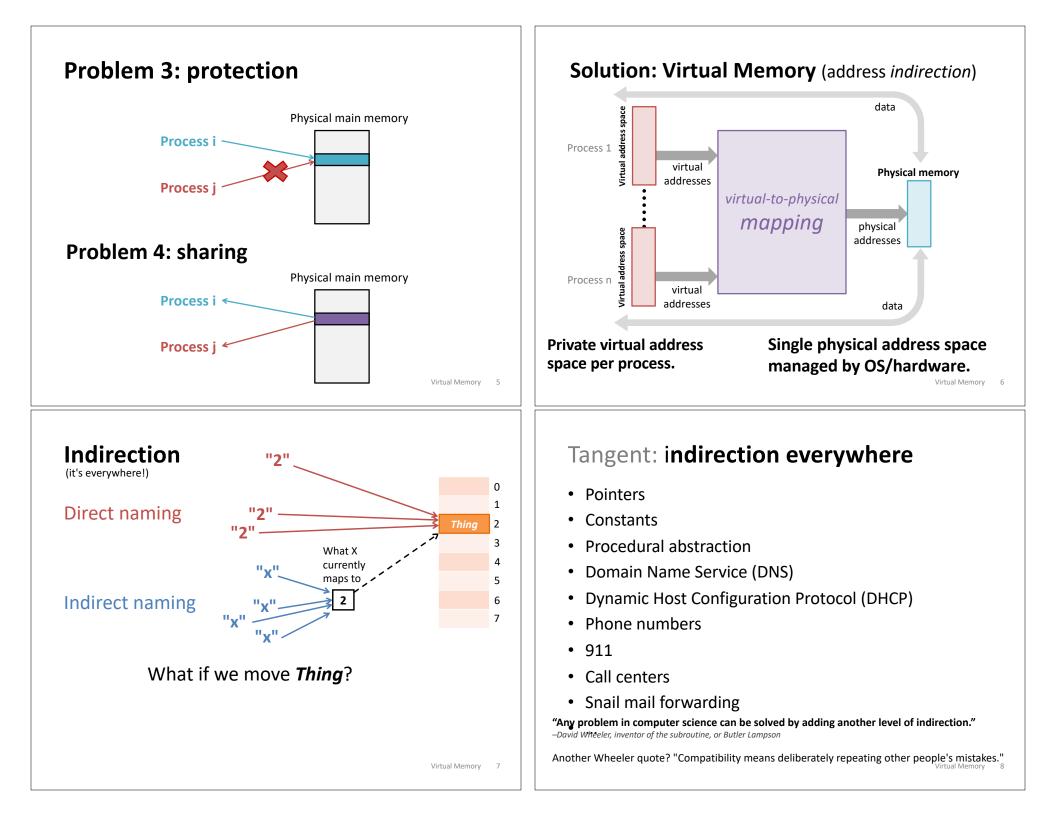

#### context switch

Switch control between processes on the same CPU.

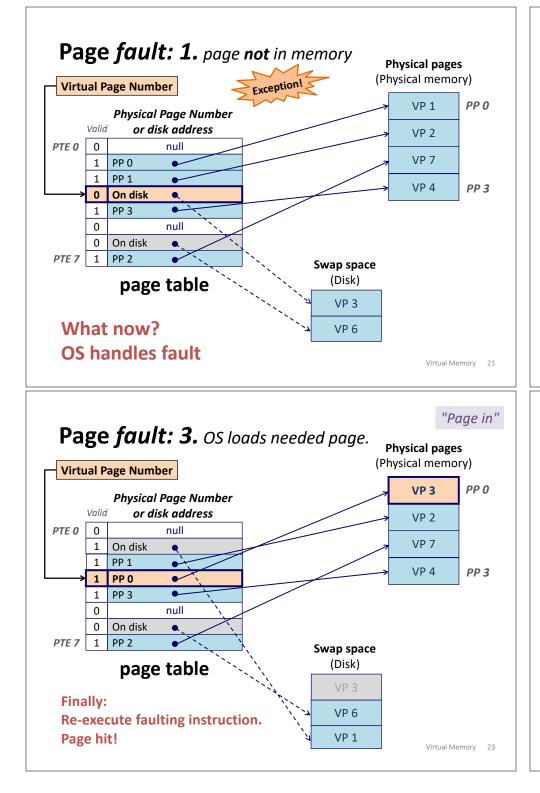

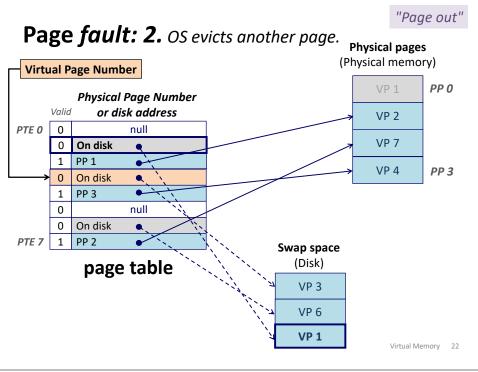

#### page in

Move page of virtual memory from disk to physical memory.

### page out

Move page of virtual memory from physical memory to disk.

### thrash

Total working set size of processes is larger than physical memory. Most time is spent paging in and out instead of doing useful work.

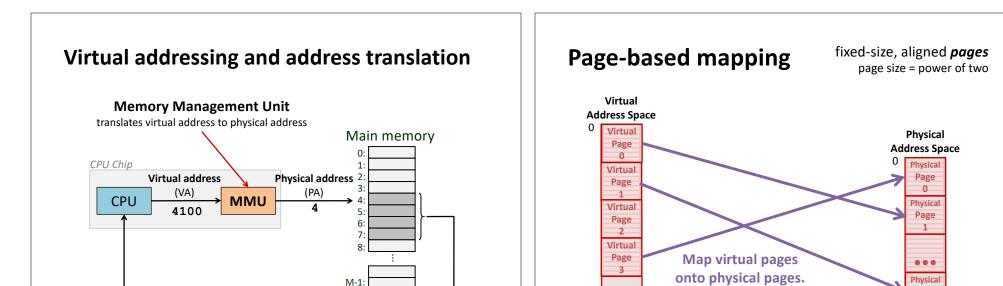

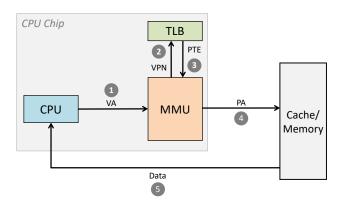

#### Address translation: page hit 2 CPU Chip PTEA 1 PTE VA Cache/ CPU MMU 3 Memory PA 4 Data 5 1) Processor sends virtual address to MMU (memory management unit) 2-3) MMU fetches PTE from page table in cache/memory 4) MMU sends physical address to cache/memory 5) Cache/memory sends data word to processor

Virtual Memory 25

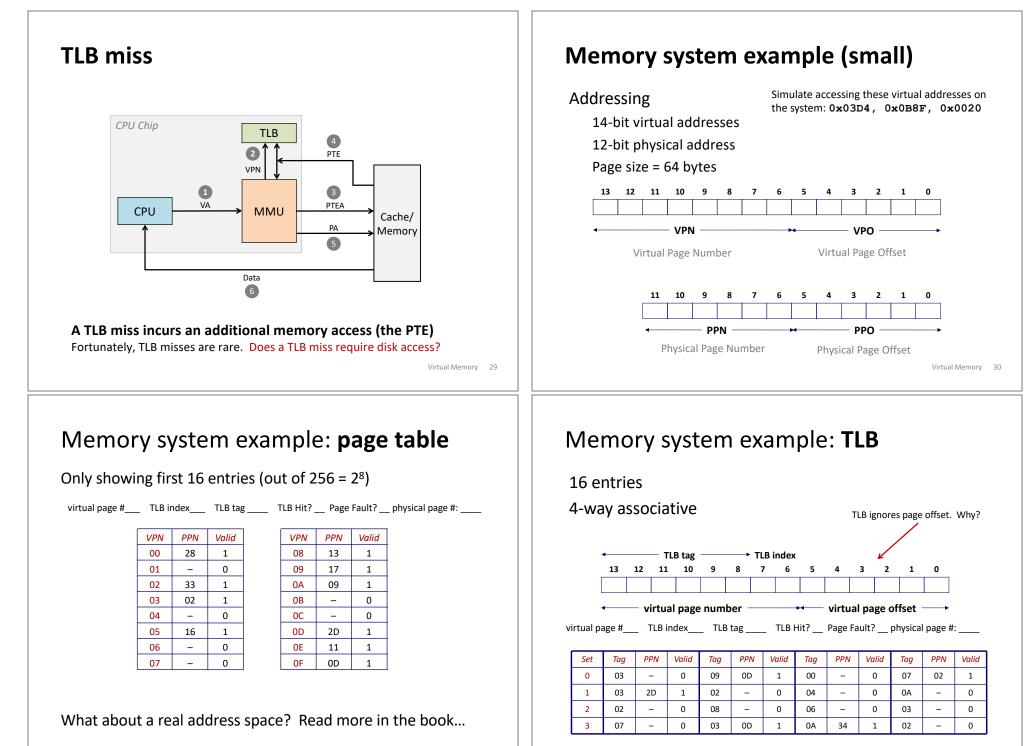

# How fast is translation?

How many physical memory accesses are required to complete one virtual memory access?

# Translation Lookaside Buffer (TLB)

Small hardware cache in MMU just for page table entries e.g., 128 or 256 entries

Much faster than a page table lookup in memory.

In the running for "un/classiest name of a thing in CS"

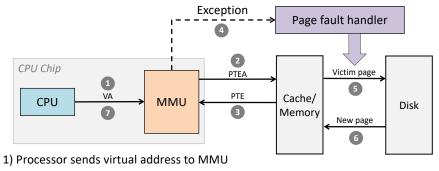

## Address Translation: Page Fault

2-3) MMU fetches PTE from page table in cache/memory

- 4) Valid bit is zero, so MMU triggers page fault exception

- 5) Handler identifies victim (and, if dirty, pages it out to disk)

- 6) Handler pages in new page and updates PTE in memory

- 7) Handler returns to original process, restarting faulting instruction

Virtual Memory 26

# TLB hit

#### A TLB hit eliminates a memory access

Virtual Memory 27

Virtual Memory 31

Virtual Memory 32

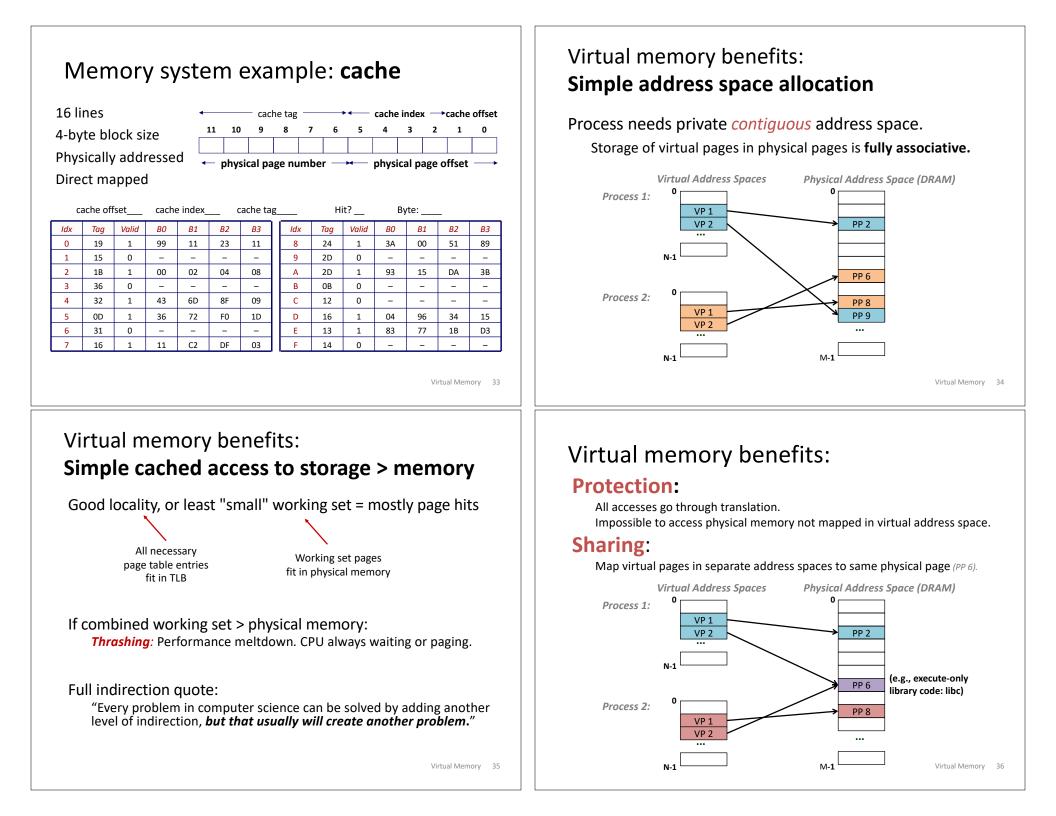

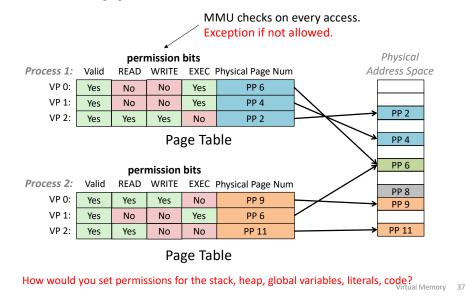

## Virtual memory benefits: Memory permissions

## Summary: memory hierarchy

### L1/L2/L3 Cache: Pure Hardware

Purely an optimization "Invisible" to program and OS, no direct control Programmer cannot control caching, can write code that fits well Virtual Memory: Software-Hardware Co-design

Supports processes, memory management Operating System (**software**) manages the mapping Allocates physical memory Maintains page tables, permissions, metadata Handles exceptions Memory Management Unit (**hardware**) does translation and checks Translates virtual addresses via page tables, enforces permissions TLB caches the mapping Programmer cannot control mapping, can control sharing/protection via OS Summary: virtual memory

## Programmer's view of virtual memory

Each process has its own private linear address space Cannot be corrupted by other processes

## System view of virtual memory

Uses memory efficiently (due to locality) by caching virtual memory pages Simplifies memory management and sharing Simplifies protection -- easy to interpose and check permissions

More goodies:

- Memory-mapped files

- Cheap fork() with copy-on-write pages (COW)

Virtual Memory 38