# Combinational Logic

Karnaugh maps

Building blocks: encoders, decoders, multiplexers

#### Recall: sum of products

logical sum (OR) of products (AND) of inputs or their complements (NOT).

| Α | В | С | M |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

#### Construct with:

- 1 code detector per 1-valued output row

- 1 large OR of all code detector outputs

Is it minimal?

#### **Gray Codes = reflected binary codes**

Alternate binary encoding designed for electromechanical switches and counting.

How many bits change when incrementing?

#### Karnaugh Maps: find (minimal) sums of products

|   |   |   |   |             | gray              | code    |             | C         | D       |           |    |

|---|---|---|---|-------------|-------------------|---------|-------------|-----------|---------|-----------|----|

| A | В |   | D | F(A, B, C,  | D) or             | der 🖰   | <b>→</b> 00 | 01        | 11      | 10        |    |

| 0 | 0 | 0 | 0 | 0           |                   | Ψ       |             |           |         |           |    |

| 0 | 0 | 0 | 1 | 0           |                   | 00      | 0           | 0         | 0       | 0         |    |

| 0 | 0 | 1 | 0 | 0           |                   |         |             |           |         |           |    |

| 0 | 0 | 1 | 1 | 0           |                   | 01      | 0           | 0         | 0       | 1         |    |

| 0 | 1 | 0 | 0 | 0           | AB                |         |             |           |         | _         |    |

| 0 | 1 | 0 | 1 | 0           |                   | 11      | 1           | 1         | 0       | 1         |    |

| 0 | 1 | 1 | 0 | 1           |                   |         |             |           |         |           |    |

| 0 | 1 | 1 | 1 | 0           |                   | 10      | 1           | 1         | 1       | 1         |    |

| 1 | 0 | 0 | 0 | 1           |                   |         |             |           |         |           |    |

| 1 | 0 | 0 | 1 | <b>1</b> 1. | Cover exactly the | e 1s by | drawing     | ; a (mini | mum) r  | number    | (  |

| 1 | 0 | 1 | 0 | 1           | maximally sized r | rectang | les who     | se dime   | ensions | (in cells | ,) |

- of are powers of 2. (They may overlap or wrap around!)

- 2. For each rectangle, make a *product* of the inputs (or complements) that are 1 for all cells in the rectangle. (minterms)

- 3. Take the *sum* of these products.

## Karnaugh Maps and Wrapping

**CD**

DB

Blocks of 1s in Karnaugh maps can wrap around sides and even 4 corners.

Give the minimal sum-of-products for the Karnaugh map to the left.

AB

The grouping and ordering of variables in a Karnaugh map doesn't matter, but the **AB/CD** ordering is easier to read from a truth table.

Convince yourself that the **AC/DB** table is equivalent to the **AB/CD** table and has the Same sum-of-products expression. In this particular AC/DB table, no wrapping is required for the rectangles!

The minimal sum-of-products expression for a Karnaugh map may not be unique.

Ambiguity is introduced when an arbitrary choice needs to be made.

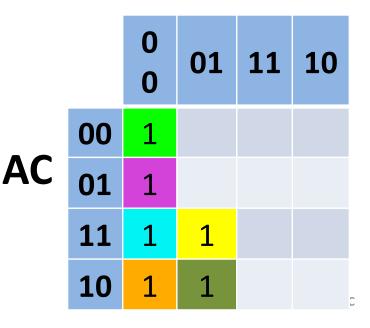

An example of ambiguity is this Karnaugh map. Give four different minimal sum-of-product expressions for this map

|    |    | CD |    |    |    |

|----|----|----|----|----|----|

|    |    | 0  | 01 | 11 | 10 |

|    | 00 | 1  | 1  | 1  | 1  |

| AB | 01 | 1  | 1  | 0  | 1  |

|    | 11 | 1  | 1  | 1  | 1  |

|    | 10 | 0  | 0  | 0  | 0  |

|    |    |    |    |    |    |

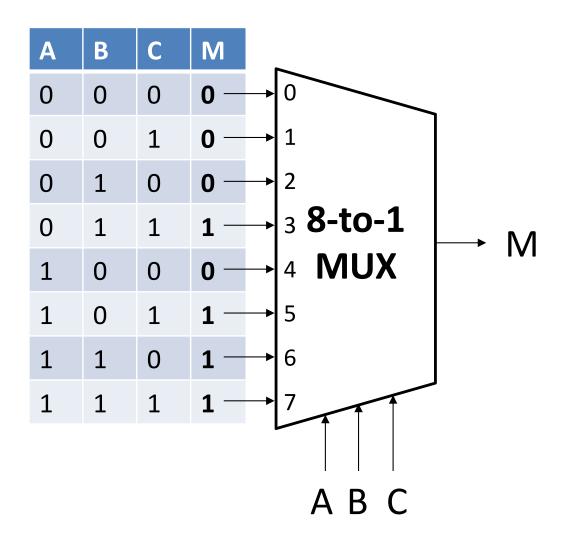

### Voting again with Karnaugh Maps

| Α | В | С | M |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

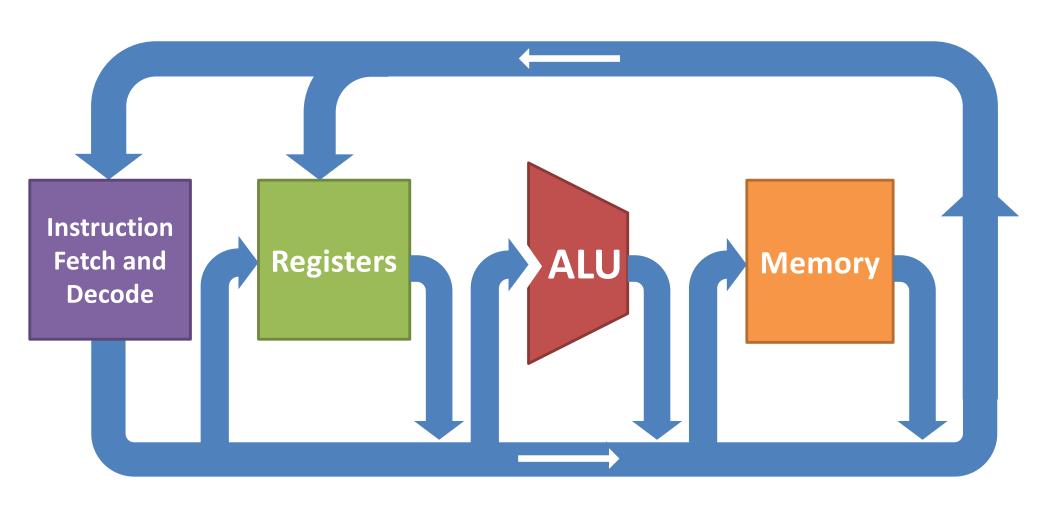

#### Goal for next 2 weeks: Simple Processor

#### **Toolbox: Building Blocks**

Microarchitecture

Processor datapath

Instruction Decoder Arithmetic Logic Unit

Memory

**Digital Logic**

Adders

Multiplexers

Demultiplexers

Encoders

Decoders

Registers

Flip-Flops Latches

Gates

Devices (transistors, etc.)

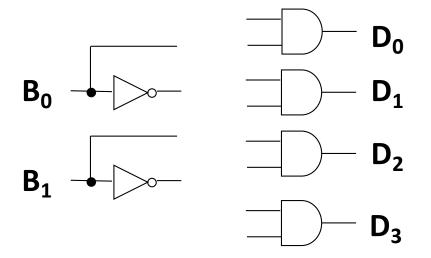

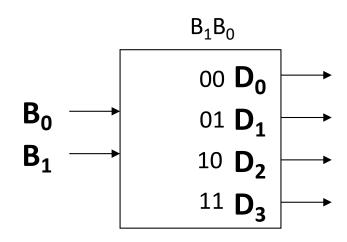

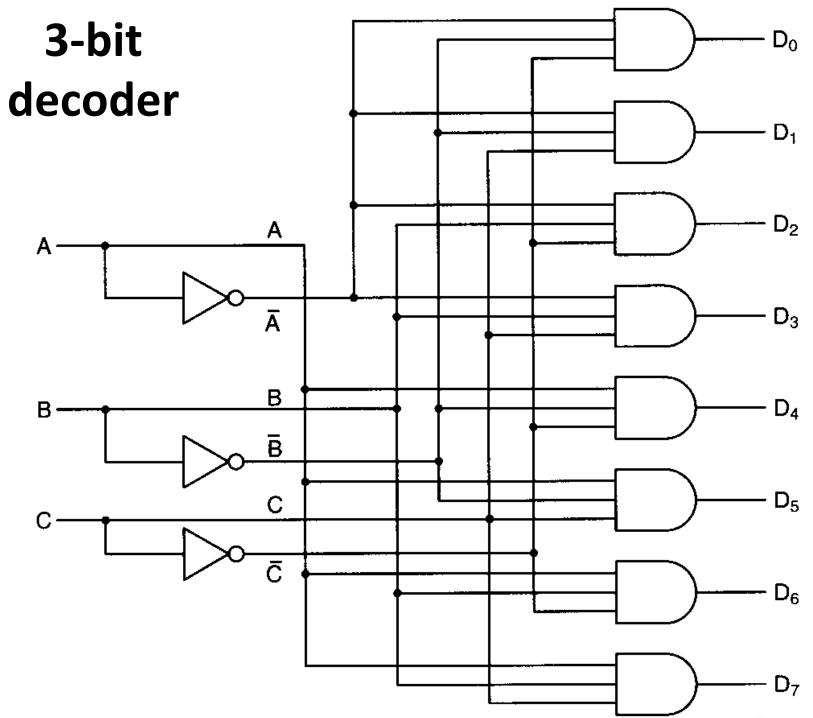

#### **Decoders**

Decodes input number, asserts corresponding output.

*n*-bit input (an unsigned number)

$2^n$  outputs

Built with code detectors.

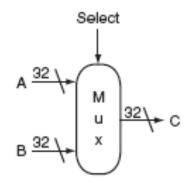

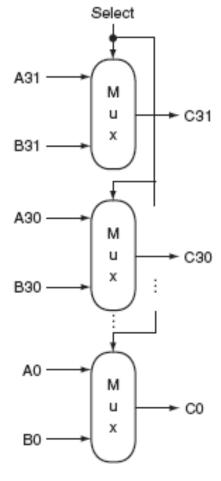

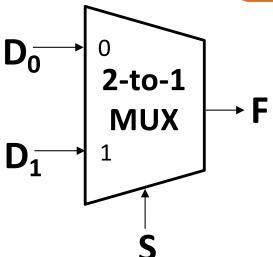

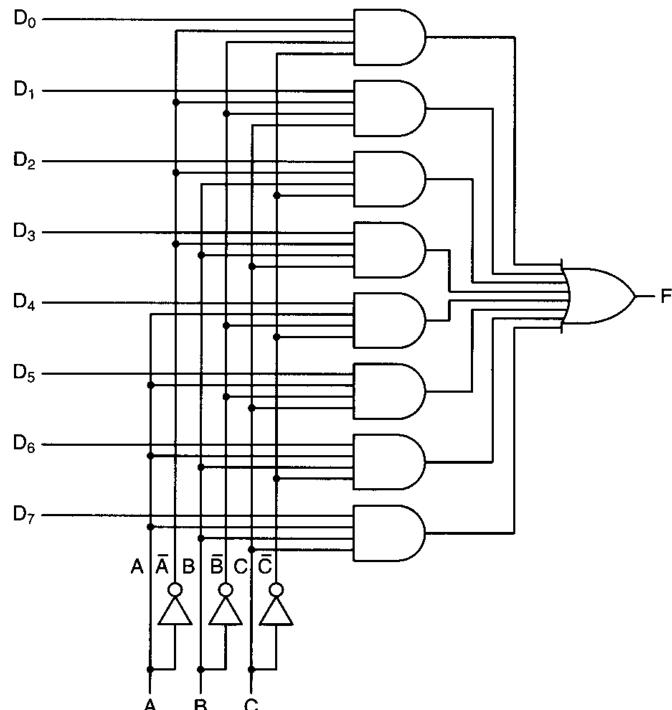

#### Multiplexers

Select one of several inputs as output.

000 001 010 011 **8-to-1** 2<sup>n</sup> data inputs 1 data output MUX 100 101 110 n selector lines

Combinational Logic

### Build a 2-to-1 MUX from gates

ех

If S=0, then  $F=D_0$ . If S=1, then  $F=D_1$ .

1. Construct the truth table.

2. Build the circuit.

#### 8-to-1 MUX

Costume idea: MUX OX

#### MUX + voltage source = truth table

#### **Buses** and **Logic Arrays**

A bus is a collection of data lines treated as a single logical signal.

= fixed-width value

Array of logic elements applies same operation to each bit in a bus.

= bitwise operator