# Sequential Logic and State

Output depends on inputs and stored values.

(vs. combinational logic: output depends only on inputs)

Elements to store values: latches, flip-flops, registers, memory

https://cs.wellesley.edu/~cs240/

Sequential Logic 1

# Sequential Logic and State

Output depends on inputs and stored values.

(vs. combinational logic: output depends only on inputs)

Elements to store values: latches, flip-flops, registers, memory

https://cs.wellesley.edu/~cs240/

Seguential Logic 2

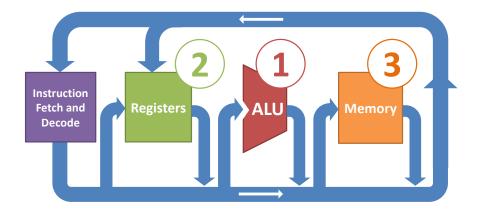

### **Processor: Data Path Components**

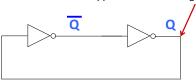

### **Unstable circuit**

Q How can Q = Q'?

Have this issue with any odd number of inverters in a loop.

Sequential Logic 3

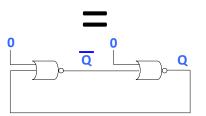

### **Bistable latches**

Things are more sensible with an even number of inverters in a loop.

Suppose we somehow get a 1 (or a 0?) on here.

Sequential Logic 5

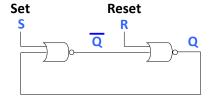

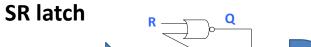

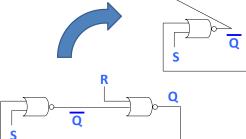

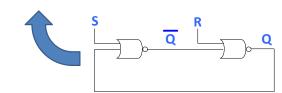

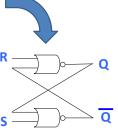

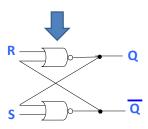

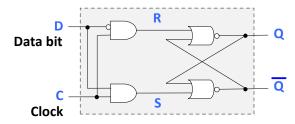

### **SR latch**

| S | R | Q <sub>prev</sub> | Q'prev | Q <sub>next</sub><br>(stable) | Q' <sub>next</sub><br>(stable) |              |                   |

|---|---|-------------------|--------|-------------------------------|--------------------------------|--------------|-------------------|

| 0 | 0 | 0                 | 1      | 0                             | 1                              |              |                   |

| 0 | 0 | 1                 | 0      | 1                             | 0                              |              |                   |

| 1 | 0 | any               | any    | 1                             | 0                              |              |                   |

| 0 | 1 | any               | any    | 0                             | 1                              |              |                   |

| 1 | 1 | any               | any    | 0                             | 0                              | <del>-</del> | ates invand Q' ar |

Sequential Logic 6

Sequential Logic 7

### D latch

if C = 0, then SR latch stores current value of Q. if C = 1, then D flows to Q:

if D = 0, then R = 1 and S = 0, Q = 0

if D = 1, then R = 0 and S = 1, Q = 1

### Notes:

- Data bit D replaces S & R: it's the bit value we want to store when Clock = 1 • Internally, Data bit D prevents bad case of S = R = 1

• This logic is **level-triggered**; as long as Clock = 1, changes to D have impact

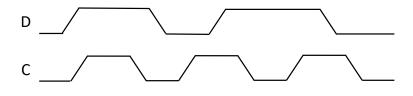

# Time matters! D C Q Assume Q has an initial state of 0

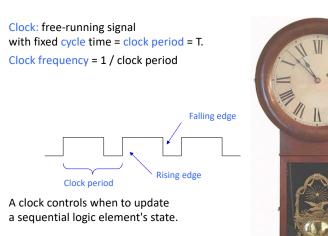

### **Clocks**

Sequential Logic 10

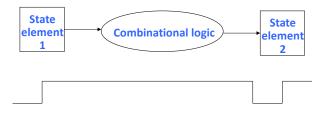

### **Synchronous systems**

Inputs to state elements must be valid on active clock edge.

Sequential Logic 11

Sequential Logic 9

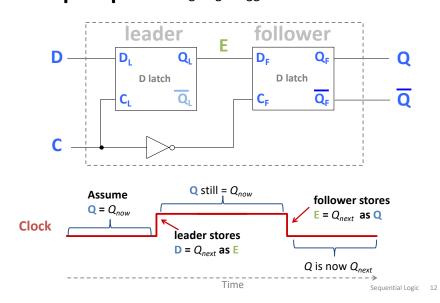

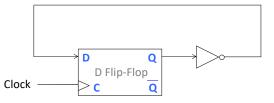

### **D flip-flop** with falling-edge trigger

### Time matters!

Ε

Q

Assume Q and E have an initial state of 0

Sequential Logic 13

### Reading and writing in the same cycle

Assume Q is initially 0.

Moral: It's OK to use the current output Q of a flip-flop as part of the the next data input D to the same flip-flop.

Sequential Logic 14

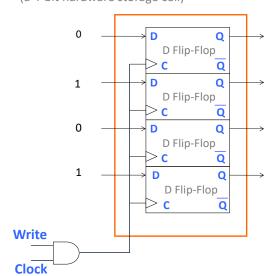

## D flip-flop = one bit of storage

The bit value of D when C has a falling edge is remembered at Q until the next falling edge of C.

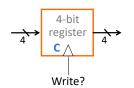

### A 1-nybble\* register

(a 4-bit hardware storage cell)

\*Half a byte!

Sequential Logic 16

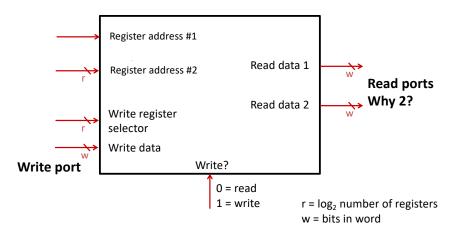

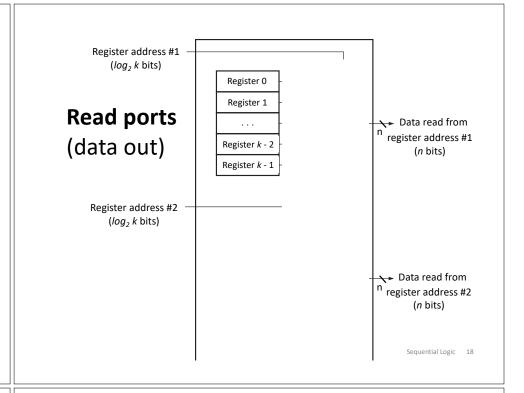

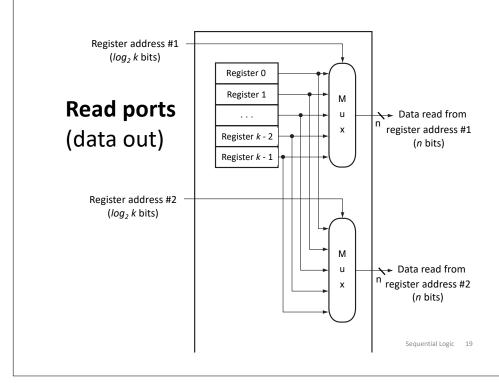

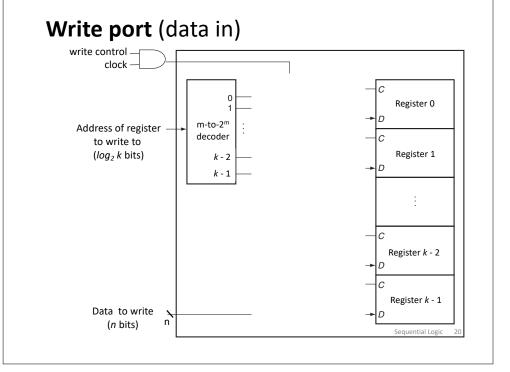

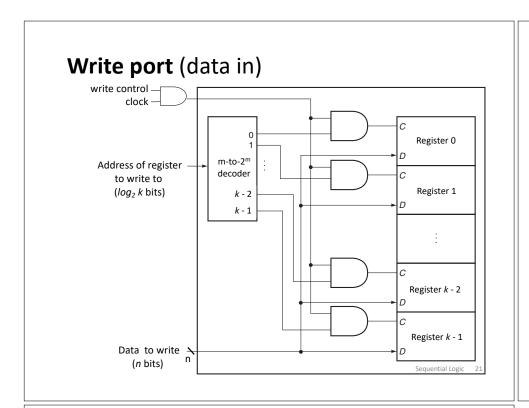

### **Register file**

Array of registers, with register selectors, write/read control, input port for writing data, output ports for reading data.

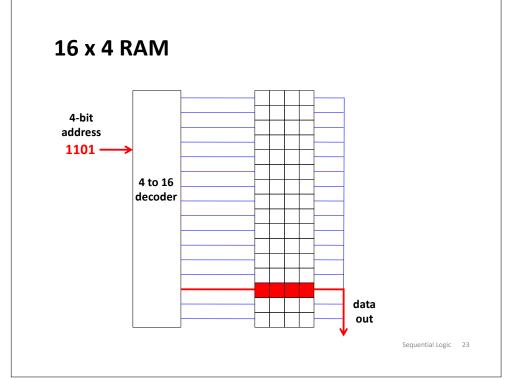

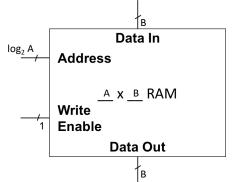

## **RAM (Random Access Memory)**

- A is number of words in RAM

- Specify the desired word by an address of size log<sub>2</sub> A

- B is the width of each word (in bits)

Similar to register file, except...