About how many hours did you spend actively working on this assignment?

| Q1 Universal Muxification of Gates [10 points] |                                                 | Time spent on Q1:                                                  |  |  |

|------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------|--|--|

| <b>1.1 NOT A</b> (one 2:1 mux) <b>[1]</b>      | <b>1.2. A AND B</b><br>(one 2:1 mux) <b>[1]</b> | 1.3 A NOR B (two 2:1 muxes) [2]                                    |  |  |

| 1.4 A XOR B (two 2:1 muxe                      | s) [Independent] [3]                            | 1.5 A XOR B (one 2:4 decoder and one 2:1 mux)<br>[Independent] [3] |  |  |

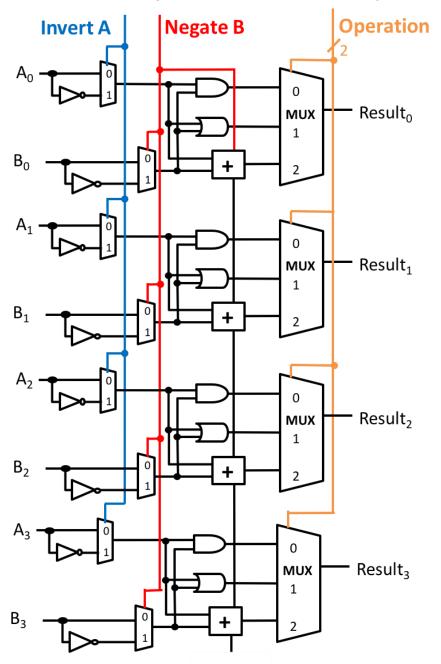

**Q2 vALUe Judgement [28 points]** Draw circuits on next page, text answers (except **2.1b**) go here.

Time spent on Q2: \_\_\_\_\_

| <b>2.1 Condition Flags [5]</b><br>(draw circuits for <b>(a)</b> and give explanation for <b>(b)</b><br>on the next page) |                    |             | ve explanatio                        | on for <b>(b)</b> | 2.3. (c) [1 point] Key reason(s) why 2.3(b) examples are incorrect.                                           |

|--------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|--------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------|

| 2.2 Result of the ALU when <i>Invert A = 1,</i><br><i>Negate B = 1,</i> and <i>Operation ID = 10.</i> [4]                |                    |             |                                      |                   |                                                                                                               |

| (a) [2] F                                                                                                                | Result =           |             |                                      |                   |                                                                                                               |

| (b) [2] [                                                                                                                | Derivatio          | on of Resul | t:                                   |                   |                                                                                                               |

|                                                                                                                          |                    |             |                                      |                   |                                                                                                               |

|                                                                                                                          |                    |             |                                      |                   | <b>2.3 (d) [3 points]</b> Draw your circuit for the Less-Than Flag on the next page.                          |

|                                                                                                                          |                    |             |                                      |                   | 2.3. (e) [1 point] Control lines for Less-Than Flag:                                                          |

|                                                                                                                          |                    |             |                                      |                   | Invert A = Negate B = Operation =                                                                             |

| <b>2.3 (a) [3 points] A, B with correct result</b> (multiple answers shown; you only needed one)                         |                    |             |                                      |                   | <b>2.3. (f) [2 points]</b> Explain why your Less-Than Flag circuit on the next page gives the correct result. |

| Α                                                                                                                        | В                  | A - B       | sign(A-B)                            | ls A < B?         |                                                                                                               |

|                                                                                                                          |                    |             |                                      |                   |                                                                                                               |

| positive                                                                                                                 | positive           |             |                                      |                   |                                                                                                               |

|                                                                                                                          |                    |             |                                      |                   |                                                                                                               |

| negative                                                                                                                 | negative           |             |                                      |                   |                                                                                                               |

|                                                                                                                          |                    |             |                                      |                   | <b>2.4. (a) [3 points]</b> Draw your Equals Flag design on the next page.                                     |

| different<br>signs                                                                                                       | different<br>signs |             |                                      |                   | 2.4. (b) [1 point] Explain why your Equals Flag                                                               |

| 2.3. (b) [2 points] A, B with incorrect result                                                                           |                    | result      | circuit correctly calculates A == B. |                   |                                                                                                               |

| Α                                                                                                                        | В                  | A - B       | sign(A-B)                            | ls A < B?         |                                                                                                               |

| nositivo                                                                                                                 |                    |             |                                      |                   |                                                                                                               |

| positive                                                                                                                 |                    |             |                                      |                   |                                                                                                               |

| negative                                                                                                                 |                    |             |                                      |                   | 2.4. (c) [1 points] Control lines for the Equals Flag                                                         |

|                                                                                                                          |                    |             |                                      |                   | Invert A = Negate B = Operation =                                                                             |

**2.1(a)** Condition Flag circuits;, **2.1(b)** explanation why Overflow Flag circuit is correct; **2.3(d)** Less-Than Flag circuit; **2.4(a)** Equals Flag circuit. Label all outputs clearly.

2.1(b) Explain why the Overflow Flag circuit is correct

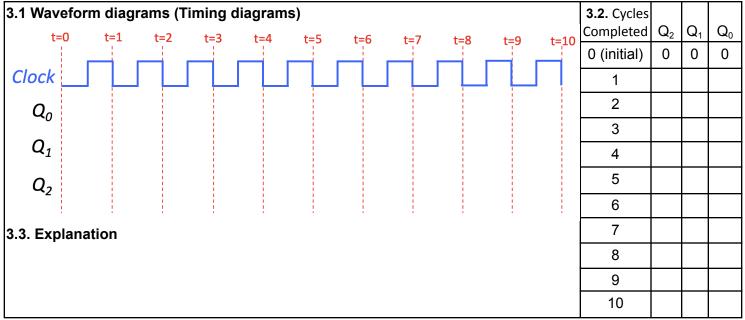

Time spent on Q3:

## Q4 Some Loopy Programs [22 points]

Time spent on Q4:

# 4.1 [8 points] Execution Table for program P1

| PC       | Instruction            |     | State Changes |     |

|----------|------------------------|-----|---------------|-----|

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

|          |                        |     |               |     |

| 4.2 [3 p | ooints] Final contents | R2: | R3:           | R4: |

4.3 [4 points] C statements equivalent to P1: // Alice starts with these C statements for program P1 int R0 = 0; int R1 = 1; int R2 = R0+R1; // Below, fill in the remaining C statements to complete program P1:

**4.4 (a)** Execute this program **P2**, assuming **R2** holds 5 and **R3** holds 4. Below, indicate the final register values when the code reaches **HALT**. (Do *not* show the step-by-step execution)

0x0: AND R2, R2, R4

0x2: AND R3, R3, R5

0x4: BEQ R5, R0, 3

0x6: SUB R5, R1, R5

0x8: ADD R4, R4, R4

0xA: JMP 2

0xC: HALT # Stops execution.

| Final register contents after executing P2 [3 points] | R2: | R3: | R4: | R5: ) |

|-------------------------------------------------------|-----|-----|-----|-------|

|                                                       |     |     |     |       |

#### 4.4(b) [2 points] C line for P2

Single line of C code equivalent to the HW ISA code for **P2**, assuming variables R2 and R3 can hold any integer values. Use only basic C operations (no conditionals, loops, or function calls).

R4 =

4.3(b) [2 points] Explanation why C line in 4.4(b) calculates the same result as program P2

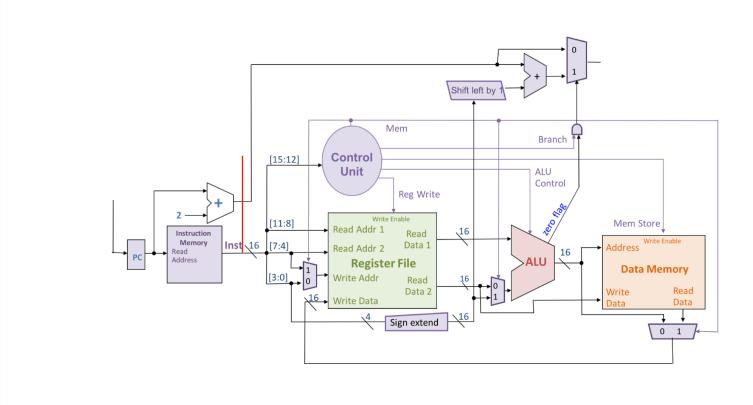

#### Q5 Taking Control [9 points]

Time spent on Q5:

## Control Unit Truth Table

| Instruction<br>Name | Opcode <sub>[3:0]</sub><br>(4 bits) | Reg Write<br>(1 bit) | ALU Op <sub>[3:0]</sub><br>(4 bits) | Mem Store<br>(1 bit) | Mem Load<br>(1 bit) | Branch<br>(1 bit) | Jump<br>(1 bit)<br><b>7.2 [1]</b> |

|---------------------|-------------------------------------|----------------------|-------------------------------------|----------------------|---------------------|-------------------|-----------------------------------|

| LW                  | 0000                                | 1                    | 0010                                | 0                    | 1                   | 0                 |                                   |

| SW                  |                                     |                      |                                     |                      |                     |                   |                                   |

| ADD                 |                                     |                      |                                     |                      |                     |                   |                                   |

| SUB                 |                                     |                      |                                     |                      |                     |                   |                                   |

| AND                 |                                     |                      |                                     |                      |                     |                   |                                   |

| OR                  |                                     |                      |                                     |                      |                     |                   |                                   |

| BEQ                 |                                     |                      |                                     |                      |                     |                   |                                   |

| NAND<br>6.2(b) [3]  |                                     |                      |                                     |                      |                     |                   |                                   |

| JMP<br>7.3 [3]      |                                     |                      |                                     |                      |                     |                   |                                   |

### Q6 Instruction Not Missing [12 points]

Time spent on Q6:

6.1 [4 points]

## 6.1(a) [1 point] Give a definition of ~X in terms of X and signed two's complement arithmetic:

~X =

**6.1(b) [3 points]** Based on the previous subpart, the instruction **NOT Rs**, **Rd** can be emulated by running the following instructions instead:

# ----- 16-bit encoding ------

| Assembly                           | Meaning                       | Opcode<br>[15:12] | Rs<br>[11:8] | Rt<br>[7:4] | Rd<br>[3:0] |

|------------------------------------|-------------------------------|-------------------|--------------|-------------|-------------|

| 6.2(a) [3 points]<br>NAND Rs,Rt,Rd | $R[d] \leftarrow ~(Rs \& Rt)$ |                   |              |             |             |

| 6.3 [2 points]<br>NOT Rs,Rd        | $R[d] \leftarrow \sim Rs$     |                   |              |             |             |

**7.1(a) [8 points].** Below, add a Jump output wire from the Control Unit and modify logic to use it to implement JMP instruction. Note: if you use the new red write split off from Inst, be sure to label which range ([?, ?]) of bits you use.

**7.2 [1 point]** For this part, fill out the Jump column in the Control Unit Truth Table in Q5.

**7.3 [3 points]** For this part, fill out the JMP row in the Control Unit Truth Table in Q5. When the bits in a cell don't matter (they can be anything), you must explicitly write this!