# **Memory Devices**

Small: Register file (group of numbered registers)

**Medium: SRAM** (Static Random Access Memory)

**Large:** DRAM (Dynamic Random Access Memory)

Future?

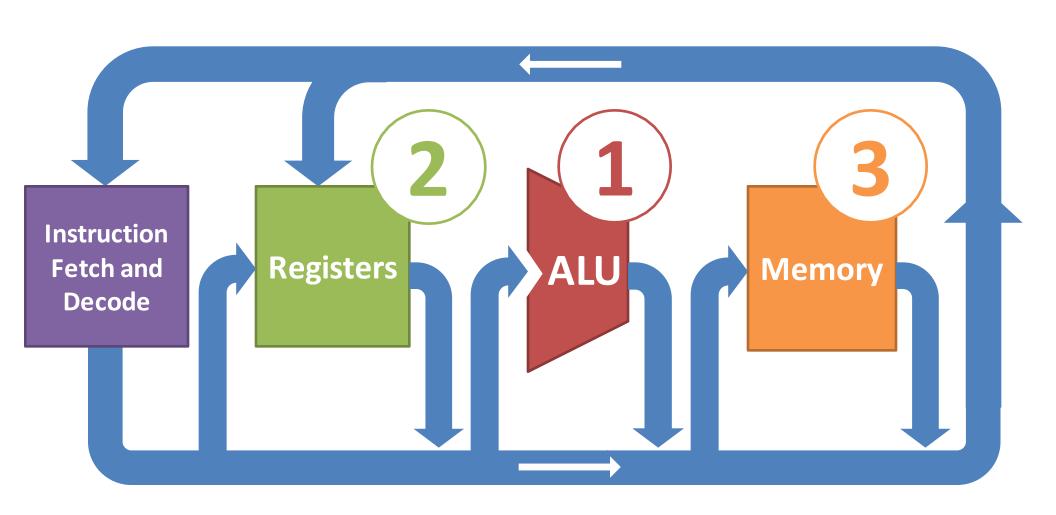

### **Processor: Data Path Components**

### **SRAM: Static Random Access Memory**

### SRAM read port: data out

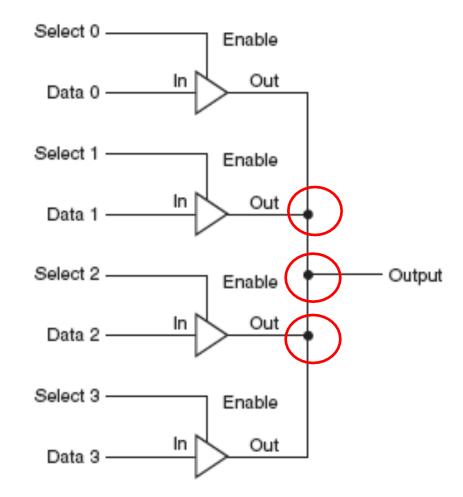

Large register files are impractical.

Big MUX = *significant* gate delay.

Large memories use a shared output line.

No central gates/MUX to choose output!

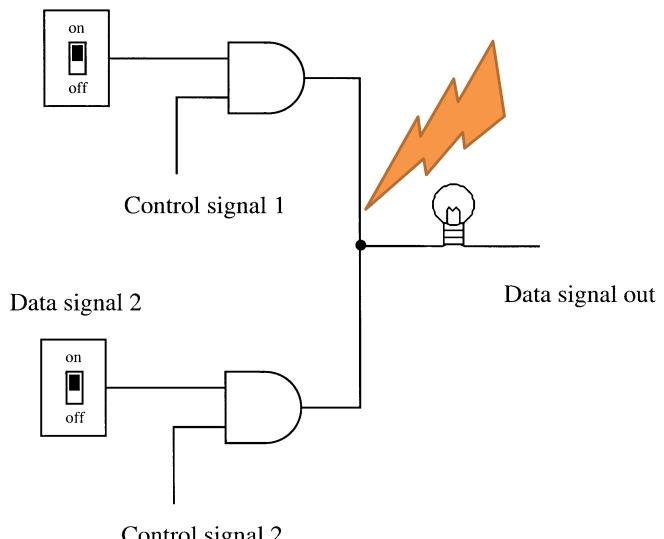

## Wired ORs (don't try this at home/in the lab, kids)

#### Data signal 1

#### Danger, Will Robinson!

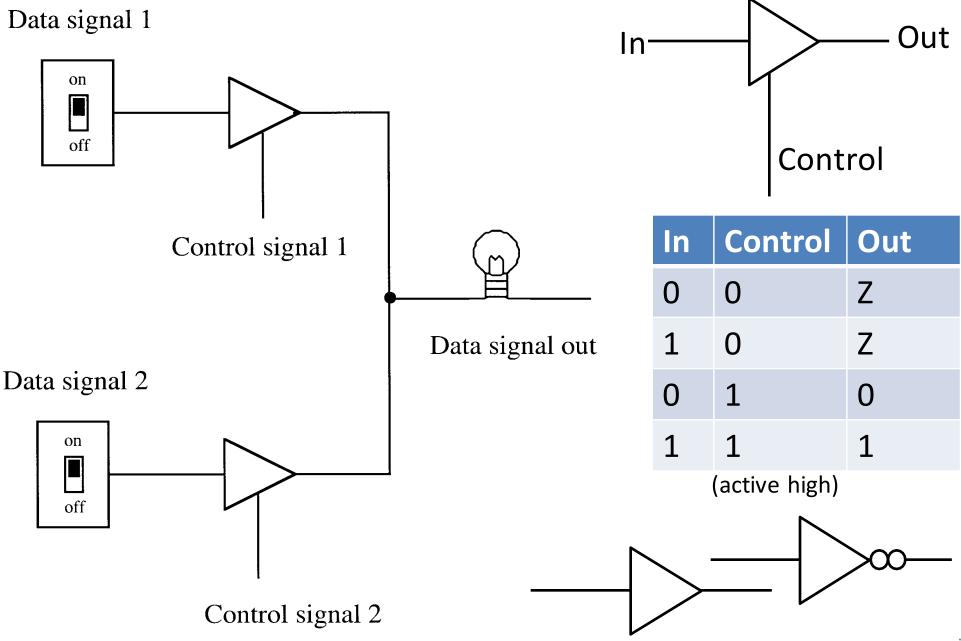

## (noninverting) tristate buffers

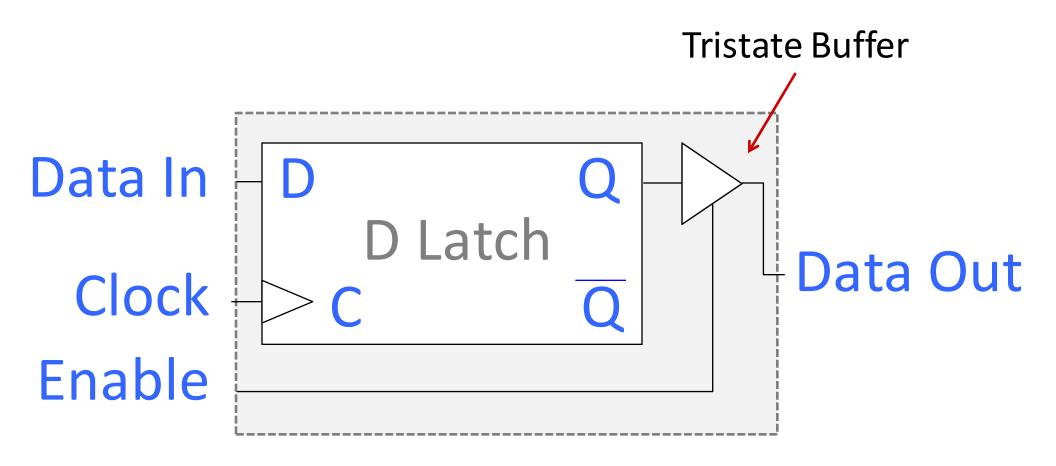

#### **SRAM** cell

one option

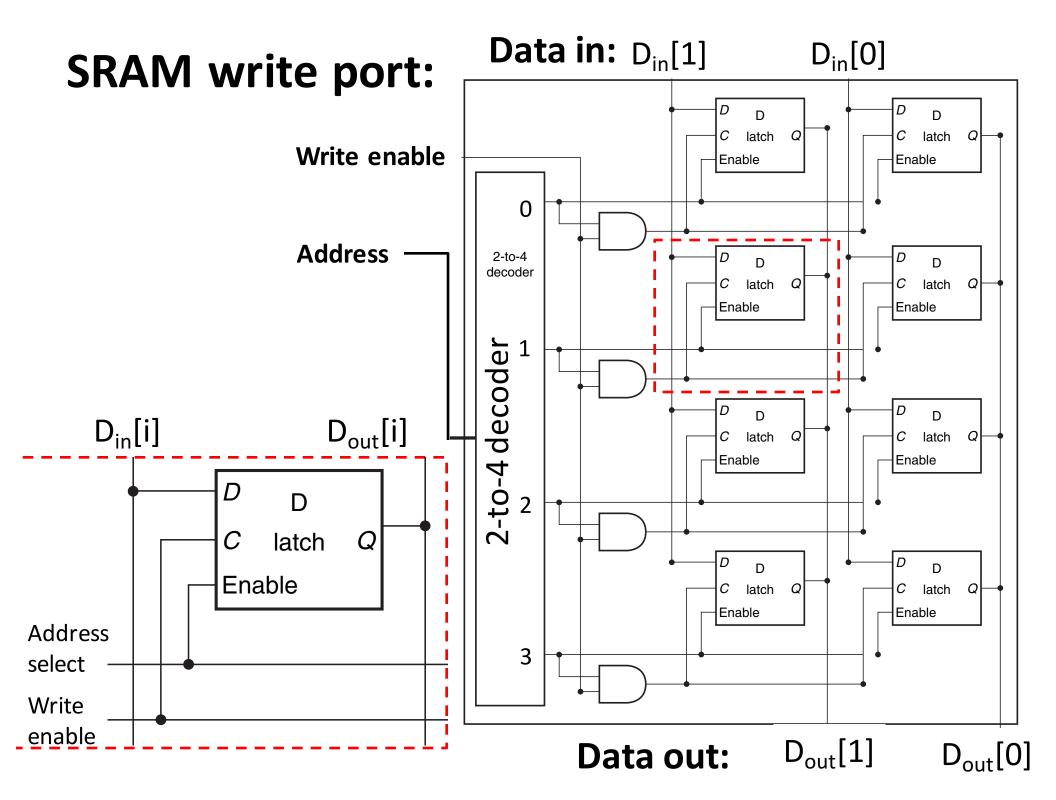

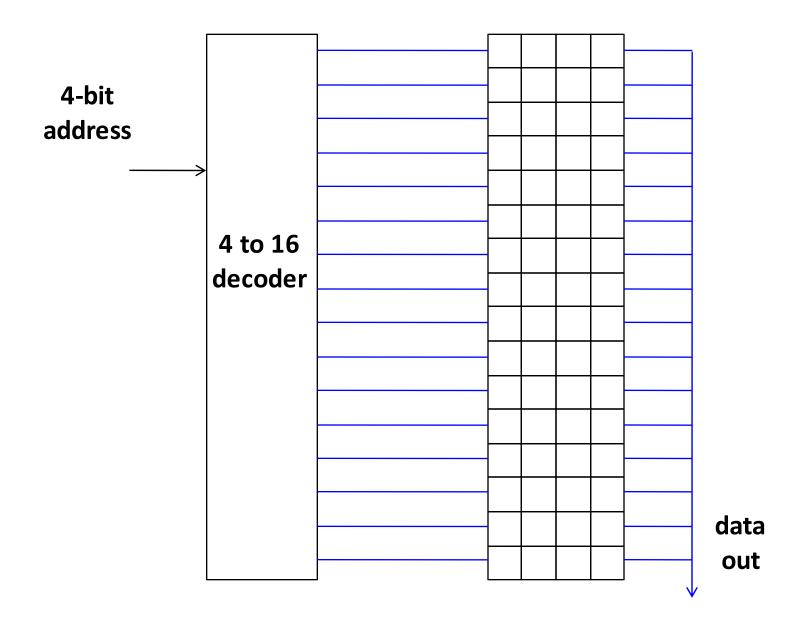

## Organization of a 16 x 4 SRAM

(one option)

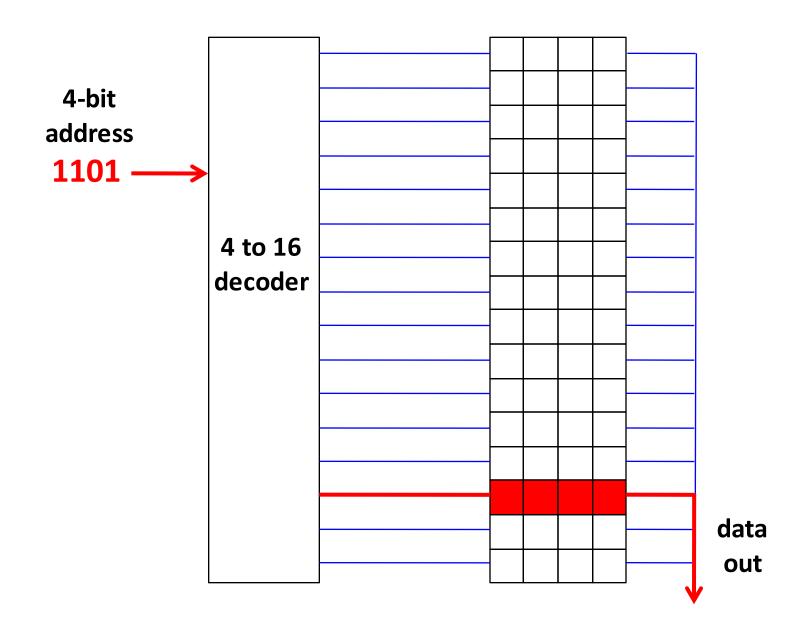

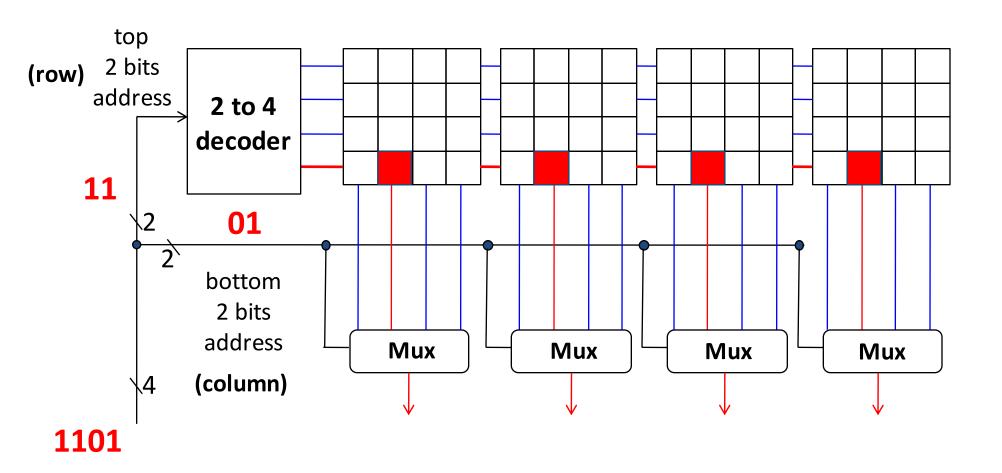

# **Selecting location 1101**

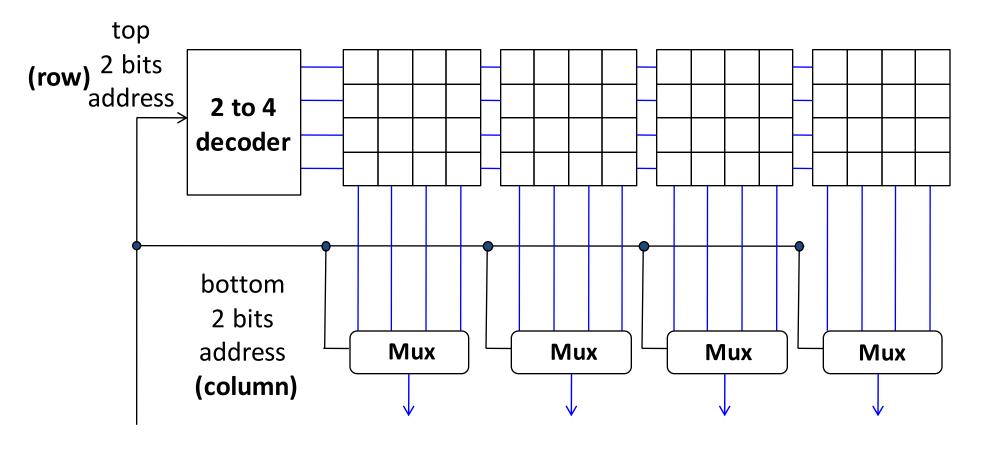

### Another organization of a 16 x 4 SRAM

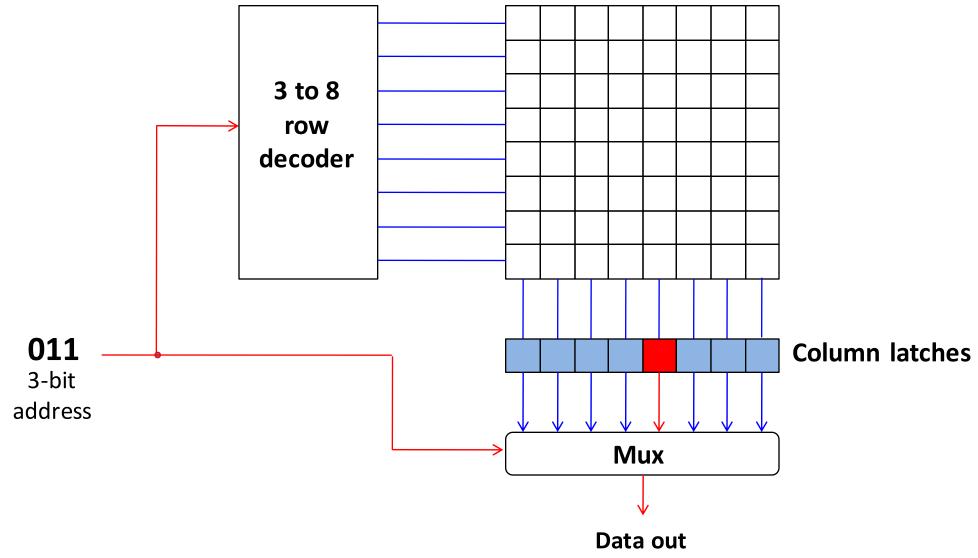

Split-level row/column addressing = physical multidimensional array!

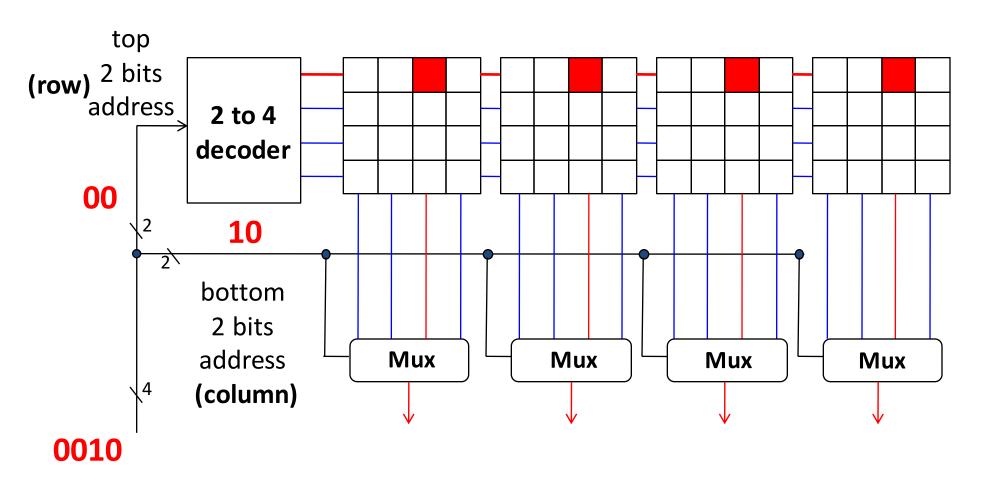

### **Selecting location 0010**

Nibbles "striped" across 4 smaller memories.

### **Selecting location 1101**

Nibbles "striped" across 4 smaller memories.

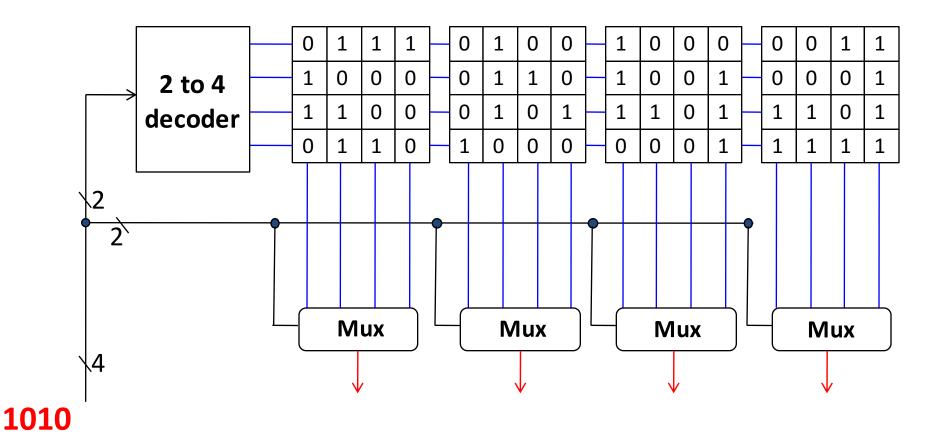

#### What value does location 1010 hold?

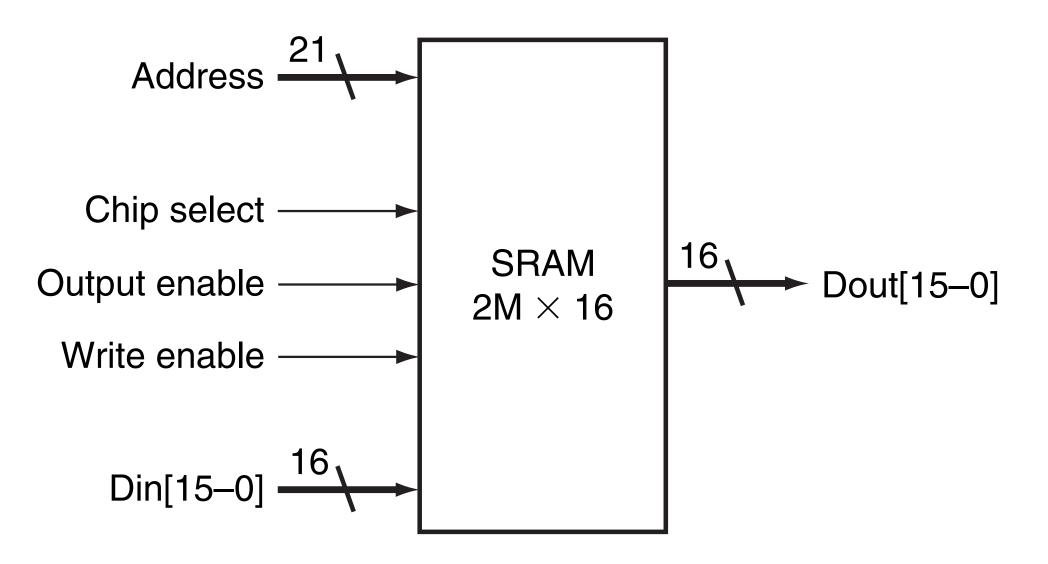

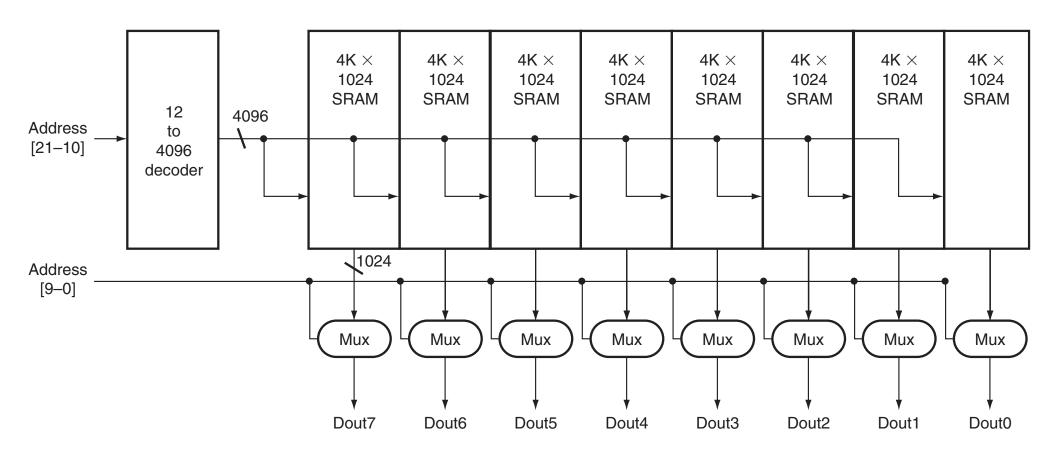

### Organization of a 4M x 8 SRAM

(one option)

= 4 MB memory, size of a large cache for modern laptop

In practice, single set of data lines often time-shared for read (out)/write (in).

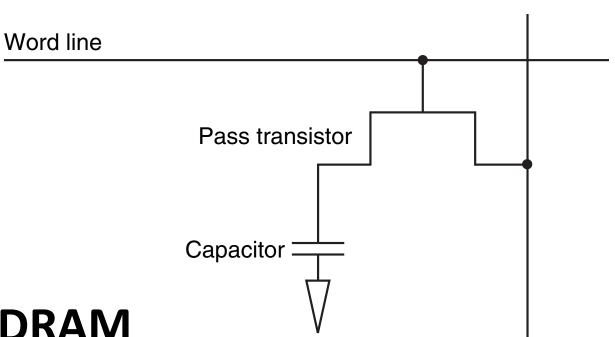

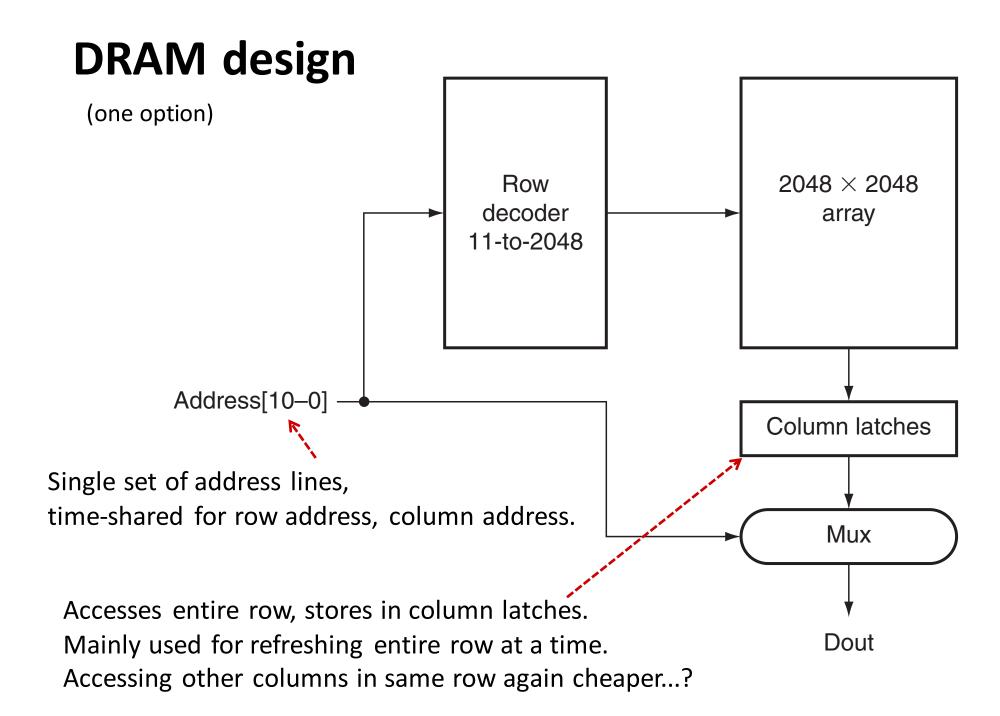

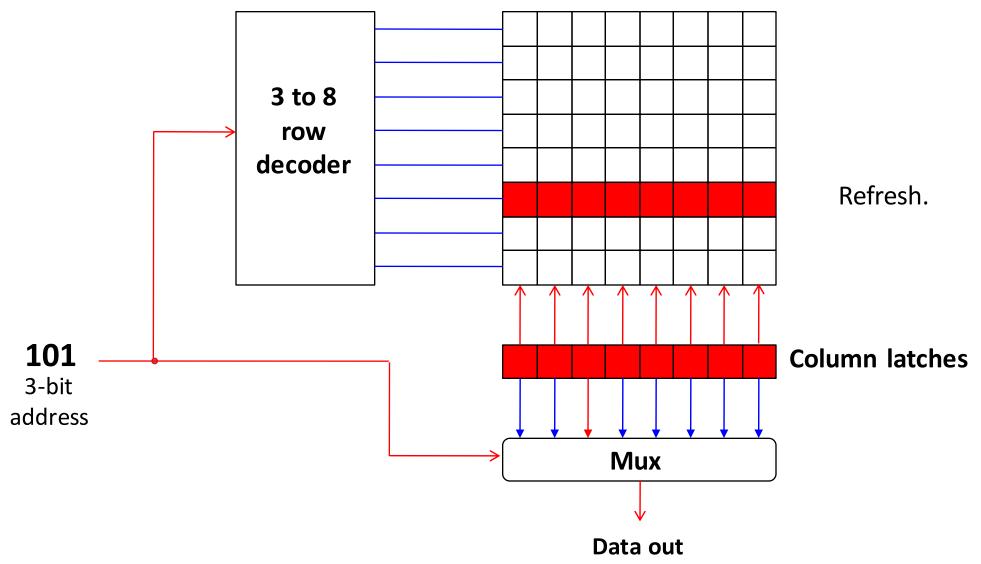

### **Dynamic RAM = DRAM**

**DRAM** stores bit as charge on capacitor:

- 1 transistor accesses stored charge.

- requires periodic refresh = read-write (dynamic power)

**SRAM** stores bit on pair of inverting gates:

- several transistors

- requires continuous (static) power.

Bit line

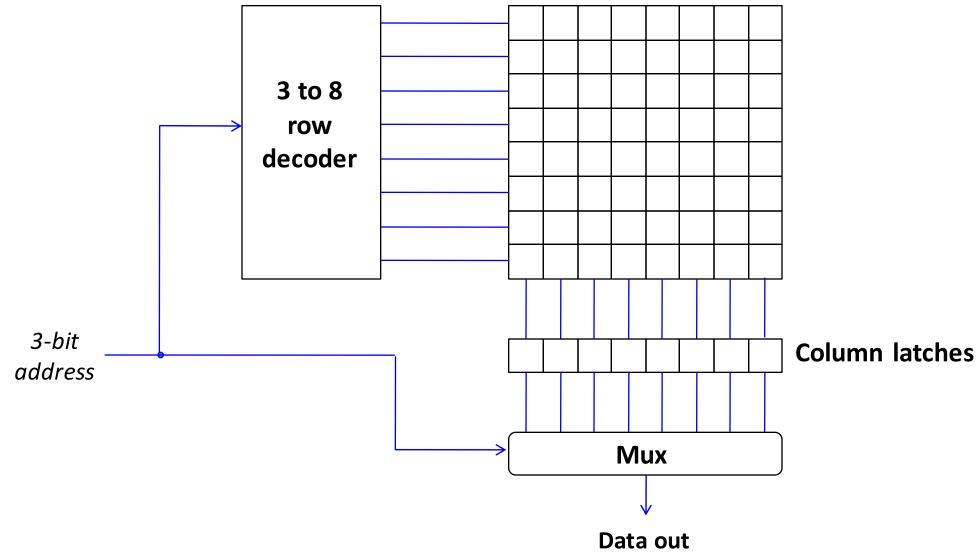

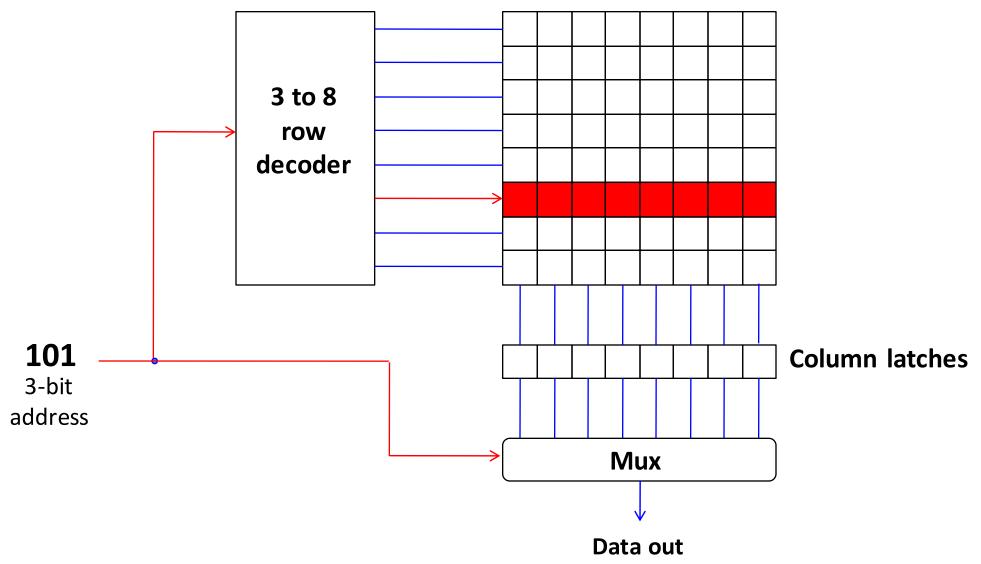

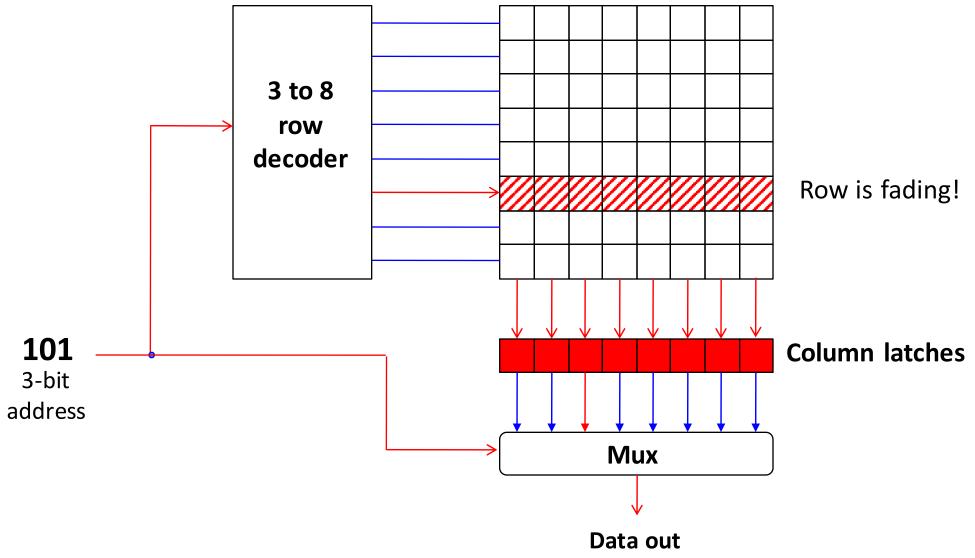

### 64-bit DRAM

#### 1. Select row

## 2. Copy row to latches

#### 3. Refresh row from latches

### 4. Select column from latches